# **Development of a Monolithic Very Large Scale Optoelectronic Integrated Circuit Technology**

by

Joseph F. Ahadian

B.S.E.E., University of California, San Diego (1993)

S.M.E.E., Massachusetts Institute of Technology (1995)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2000

© 2000 Massachusetts Institute of Technology All Rights Reserved.

• • •

# **Development of a Monolithic Very Large Scale Optoelectronic Integrated Circuit Technology**

by

Joseph F. Ahadian

Submitted to the Department of Electrical Engineering and Computer Science on December 17, 1999, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

# Abstract

Optical interconnects have been proposed for use in high-speed digital systems as a means of overcoming the performance limitations of electrical interconnects at length scales ranging from one millimeter to one hundred meters. To achieve this goal, an optoelectronic very large scale integration (OE-VLSI) technology is needed which closely couples large numbers of optoelectronic devices, such as light emitters and photodetectors, with complex electronics. This thesis has been concerned with the development of an optoelectronic integration technology known as Epitaxy-on-Electronics (EoE). EoE produces monolithic optoelectronic integrated circuits (OEICs) by combining conventional epitaxial growth and fabrication techniques with commercial GaAs VLSI electronics. Proceeding from previous feasibility demonstrations, the growth and fabrication practices underlying the EoE integration process have been extensively revised and extended. The effectiveness of the resulting process has been demonstrated by fabricating the first monolithic, VLSI-complexity OEICs featuring light-emitting diodes (LEDs). As part of a research foundry project, components of this type were designed and tested by a number of groups involved in optical interconnect system development. To further realize the potential of the EoE technology, and to make its capabilities accessible to a broader user community, the focus of this work was extended beyond the development of the integration process to encompass a study of high-speed photodetectors implemented in the GaAs VLSI process, to examine the role of the EoE technology within optical interconnect applications, to formulate an analytical framework for the design of digital optical interconnects, and to implement compact, low power laser driver and optical receiver circuitry needed to implement these interconnects.

Thesis Supervisor: Clifton G. Fonstad, Jr. Title: Professor of Electrical Engineering

# Acknowledgements

I would, first of all, like to thank my thesis advisor, Professor Clifton. G. Fonstad, Jr. I admire Professor Fonstad for the breadth and depth of his insight, for his lack of pretense, and for his kindness and sincerity. I am very grateful for the opportunity he has given me to learn and grow over the last six and one-half years. I would like to also thank my thesis committee members, Professors Akintunde "Tayo" Akinwande and Charles G. Sodini, for undertaking the daunting task of reading this document, for their keen observations, and for their encouragement.

This project would not have been possible without the involvement of Vitesse Semiconductor Corporation co-founder and chief technical officer James M. Mikkelson. Aside from providing access to Vitesse's people and technology, he has, over countless telephone conversations, been a source of clarity in every phase of this work. There are many people at Vitesse to whom I am thankful, but I would like to especially acknowledge Max Helix for shepherding my handiwork through the fab in Camarillo, Robert N. Deming for helpful circuit-design consultations, and Paul Partyka for useful discussions about photodetectors.

Another key to the successful completion of this thesis has been Professor Leslie A. Kolodziejski. Her involvement, which began as my master's thesis co-advisor and continued through the demonstration of integrated light emitting diodes, is greatly appreciated.

I owe numerous thanks to Dr. Gale S. Petrich. Charged with maintaining both the Kolodziejski molecular beam epitaxy facility and the "micro lab" fabrication facility, and as the designated troubleshooter and editor for anything needs to be repaired or proofread (including this thesis), he is, in my reckoning, the most important person in Building Thirteen.

This project began with the thesis work of Dr. Krishna V. Shenoy. He laid its foundations and gave me a start for which I am greatly indebted. Over the years, this project has also benefited from the hard work of Eric K. Braun, who unraveled the mysteries of GaAs VLSI thermal stability, Praveen T. Vaidyanathan, who toiled to develop light emitting diode integration processes and characterized the resulting devices, Steven G. Patterson, who languished in a cold, dark room growing the material that was needed, and Dr. Yakov Royter, whose help with circuit design, etching, and metallization rounded out the OPTOCHIP effort. Thank you all.

The OPTOCHIP project benefited from the skills of many collaborators. Two individuals whom I have come to know through this project, Professor Barry L. Shoop of the United States Military Academy and Professor Charles B. Kuznia of the University of Southern California, have lent extensively of their initiative and productivity and have been a source of much-appreciated support and encouragement. Also, for their involvement in receiver array characterization, I am grateful to Dr. Tomasz Maj and the team at McGill University and to Dr. John A. Trezza of Sanders.

I have also benefited greatly from the generosity of Donald A. Hitko and Daniel R. McMahill. I'd like to thank them for their help in understanding circuit design and board layout, and for access to Professor Sodini's equipment.

I would like to also thank all the of the past and present members of Professor Fonstad's research group for seeing to all the thankless chores that have to be done before the work starts, and for providing well-needed distractions. I would particularly like to thank Dr. Isako Hoshino, Donald S. Crankshaw, and Wojciech P. Giziewicz whom I have successively conscripted into the position of system administrator.

This thesis marks the end of my career as a professional student. I've had a lot of wonderful teachers in the last twenty-two and one-half years, There are too many to list, but in addition to Professor Fonstad, I would like to mention three that have helped to define my path. George Stimson taught me physics at San Dieguito high school, shared my excitement for applying it, and told great stories. Robert Whyte, gave up his free time to help me with a term project for Mr. Stimson's class and taught me enough engineering to put four years of college into perspective. In those four years, at the University of California, San Diego, I was given the opportunity to work in the laboratory of Professor Charles W. Tu. This experience set the direction of my graduate work.

Many of the people mentioned above have crossed the line from colleague or teacher to friend. To their names I would like to add Dr. Rajni J. Aggarwal, Dr. David J. Carter, Espartaco Hidalgo, Dr. Dionisios Margetis, Dr. Edward McKigney, Courtney C. Lane, Joanna M. London, Dr. Vernon E. Shrauger, and Karen Young-Waithe. Each of you has touched my life in an important way.

Finally, for their love and support, I would like to thank my mother and father, Mehrdokht and Faradjollah, my sister and brother, Farzaneh and Farshad, and, last but not least, Kaveri. I hope to make you as proud of me as I am of each of you.

# Contents

| 1 | Intr                                                                                                               | oduction                                                                                                                                                                                                                                          |

|---|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1<br>1.2<br>1.3                                                                                                  | Electrical and Optical Interconnects                                                                                                                                                                                                              |

| 2 | The                                                                                                                | Epitaxy-on-Electronics Integration Process                                                                                                                                                                                                        |

|   | <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol> | Thermal Stability54Historical Development58Dielectric Growth Window Preparation61Low Temperature Native GaAs Oxide Removal67Reduced Temperature MBE Growth69Polycrystalline Deposit Removal75Optoelectronic Device Fabrication78Completed OEICs79 |

| 3 | Inte                                                                                                               | grated LEDs and the OPTOCHIP Project                                                                                                                                                                                                              |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | LED fabrication process.87Bulk LEDs94The OPTOCHIP project.101Integrated LED and OEIC results.113Optical Crosstalk125Lessons From OPTOCHIP129                                                                                                      |

| 4 | Vite                                                                                                               | sse MSM Photodetectors                                                                                                                                                                                                                            |

|   | 4.1<br>4.2<br>4.3<br>4.4                                                                                           | MSM Photodetectors in the Standard Vitesse H-GaAs III Process                                                                                                                                                                                     |

| 5 | Digital Optical Interconnect Systems                                                                                                                                                           |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.1Epitaxy-on-Electronics OEIC Applications.1865.2Characteristics of Optical Link Components1915.3Digital Interconnects and Communication Channels1955.4Digital Optical Interconnect Design200 |

|   | 5.5 Transmitter and Receiver Circuit Requirements                                                                                                                                              |

| 6 | A Low Power Laser Driver                                                                                                                                                                       |

|   | <ul> <li>6.1 First-generation Switched Current Mirror Laser Driver</li></ul>                                                                                                                   |

|   | 6.5Switching Characteristics2646.6Eye Patterns, Delay Asymmetry, and Jitter2786.7Combined Laser Driver and VCSEL Characteristics2986.8Third-generation Laser Driver Designs3226.9Conclusion335 |

| 7 | A Low Power Optical Receiver                                                                                                                                                                   |

|   | 7.1       Design of a Low-Power Continuous-Time Optical Receiver                                                                                                                               |

| 8 | Conclusion                                                                                                                                                                                     |

|   | 8.1       Accomplishments                                                                                                                                                                      |

| A | Vitesse GaAs VLSI MESFET Technology                                                                                                                                                            |

| B | EoE Fabrication                                                                                                                                                                                |

| С | Circuit Characterization Setups                                                                                                                                                                |

| D | Jitter                                                                                                                                                                                         |

| E | MESFET Drain-Lag                                                                                                                                                                               |

## Contents

| F   | First-Generation Optical Receiver   | • | ••• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 447 |

|-----|-------------------------------------|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| G   | Receiver-Array OEICs                | • | ••• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 455 |

| H   | A Fully-Differential Array Receiver | • | ••• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 483 |

| I   | A Clocked Optical Receiver          | • | ••• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 497 |

| Bil | Bibliography                        |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

Contents

| 1.1  | The interconnect hierarchy                                                             |

|------|----------------------------------------------------------------------------------------|

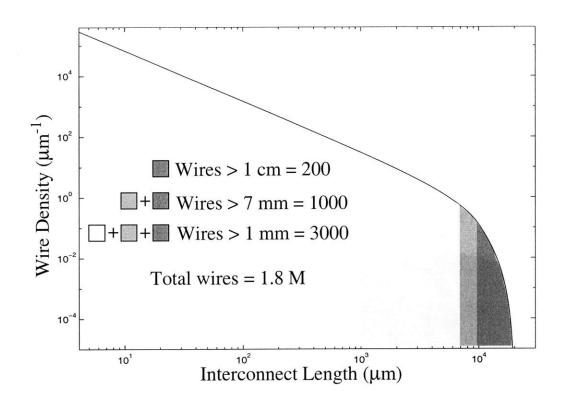

| 1.2  | Interconnect length distribution of the Intel Pentium II microprocessor                |

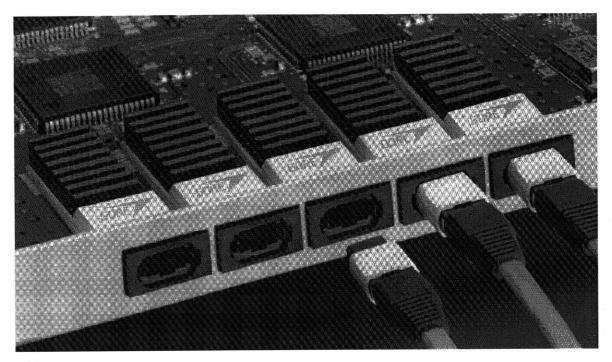

| 1.3  | A parallel fiber optic data link (W. L. Gore & Associates)                             |

| 1.4  | An optical backplane (Ericsson "flex-foil")                                            |

| 1.5  | A planar lightwave circuit (Motorola)                                                  |

| 1.6  | A free-space optical interconnect demonstration (University of Southern California) 32 |

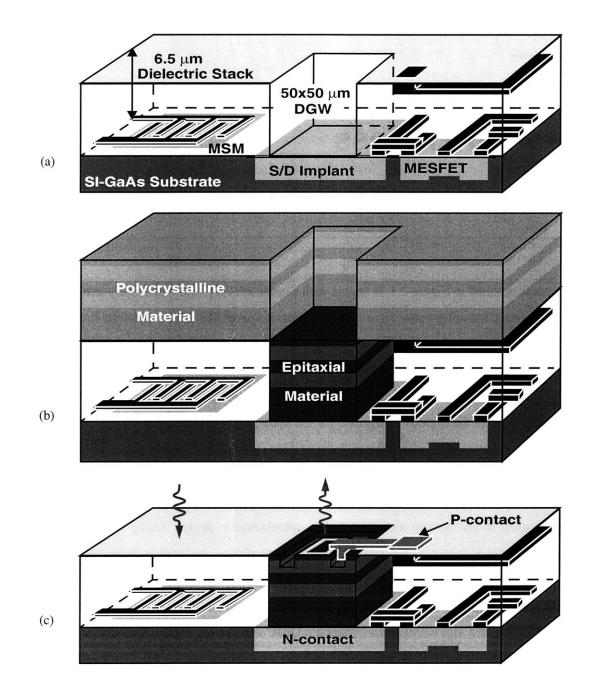

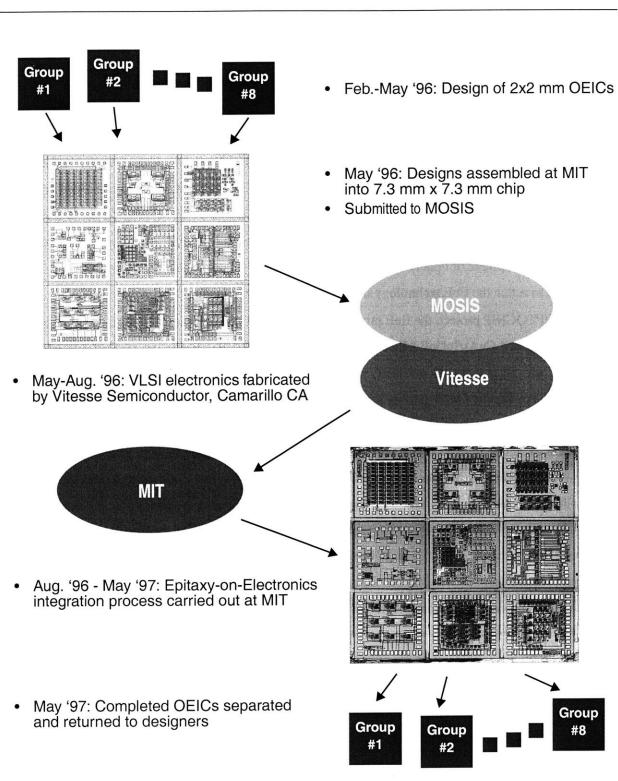

| 2.1  | Overview of the Epitaxy-on-Electronics integration process                             |

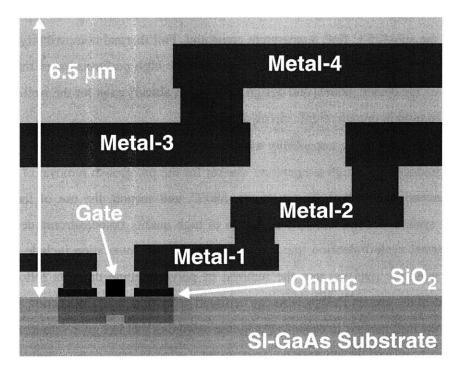

| 2.2  | Metallization on Vitesse H-GaAs III and H-GaAs IV processes                            |

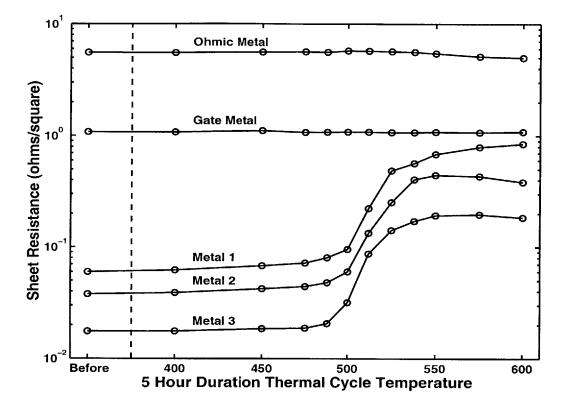

| 2.3  | Vitesse interconnect sheet resistance after 5 hour thermal cycles                      |

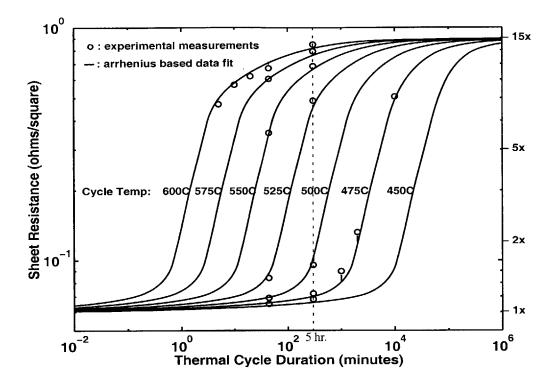

| 2.4  | Metal 1 sheet resistance thermal stability model                                       |

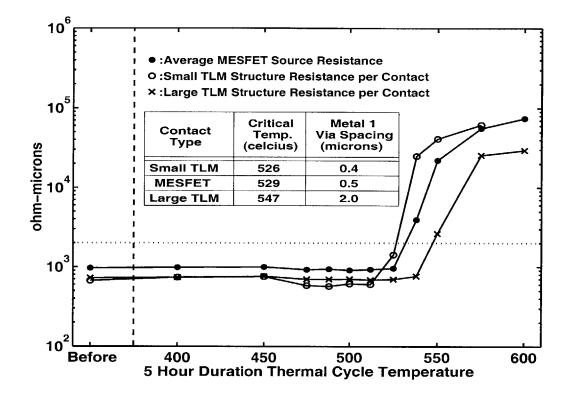

| 2.5  | Ohmic contact resistance after 5 hour thermal cycles                                   |

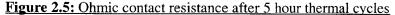

| 2.6  | Metal 1-ohmic metal-implant contact resistance thermal stability model                 |

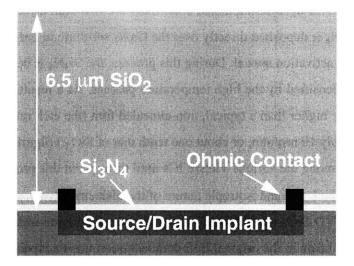

| 2.7  | The dielectric stack on Vitesse integrated circuits                                    |

| 2.8  | Initial DGW preparation technique                                                      |

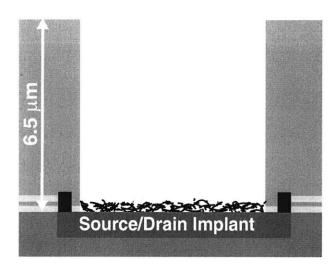

| 2.9  | DGWs contaminated by RIE residues                                                      |

| 2.10 | DGW preparation technique based on partial RIE etch of dielectric stack                |

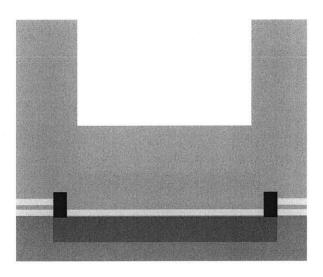

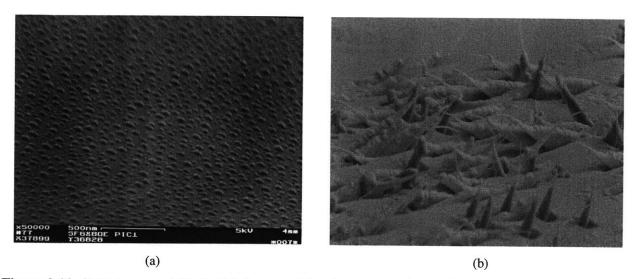

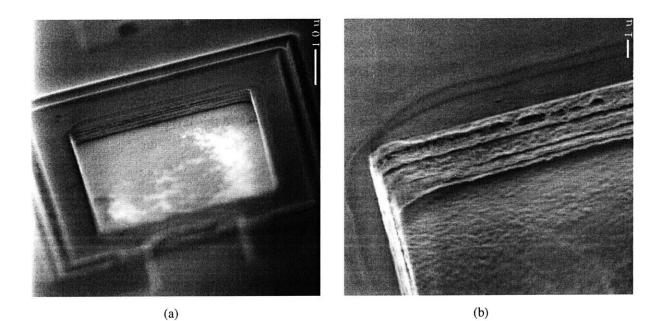

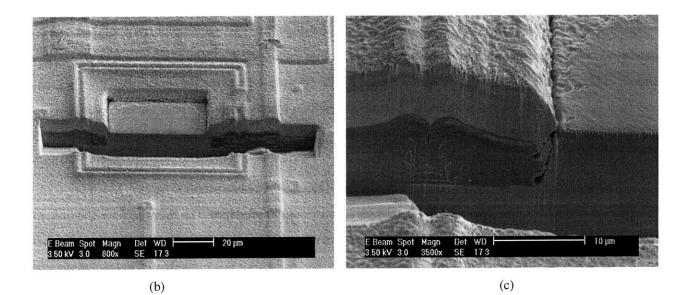

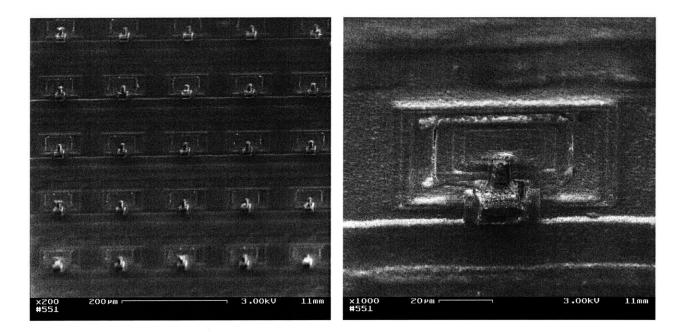

| 2.11 | SEM images of "Spike" defects resulting from contaminated dry processing               |

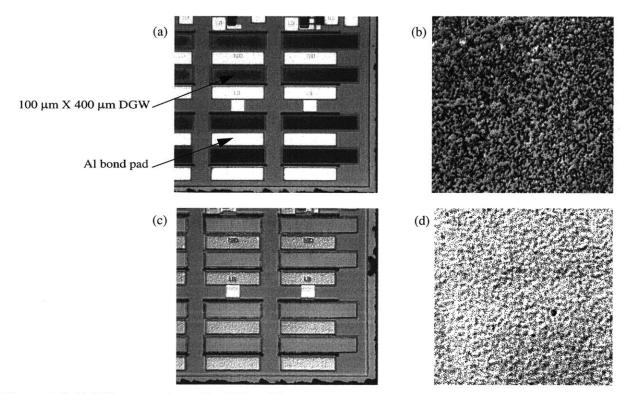

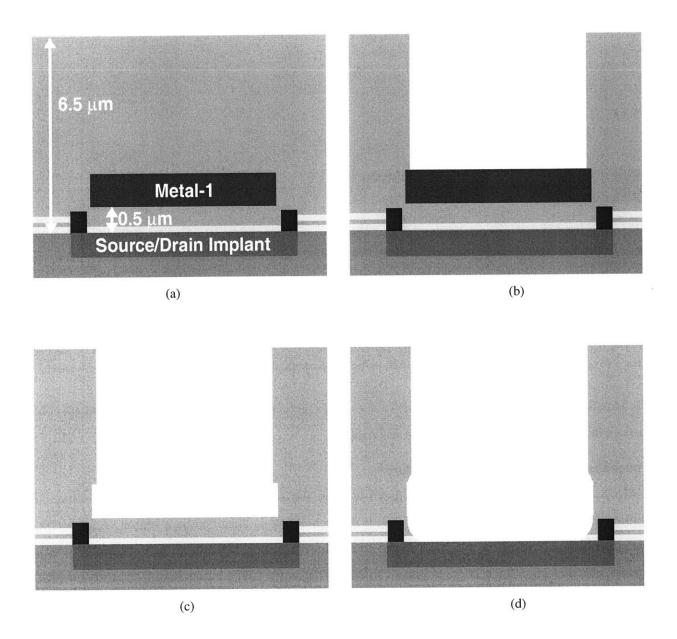

| 2.12 | Successful DGW preparation process                                                     |

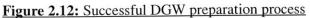

| 2.13 | SEM of DGW on an OEIC as received from Vitesse/MOSIS                                   |

| 2.14 | SEM of nearly completed DGW                                                            |

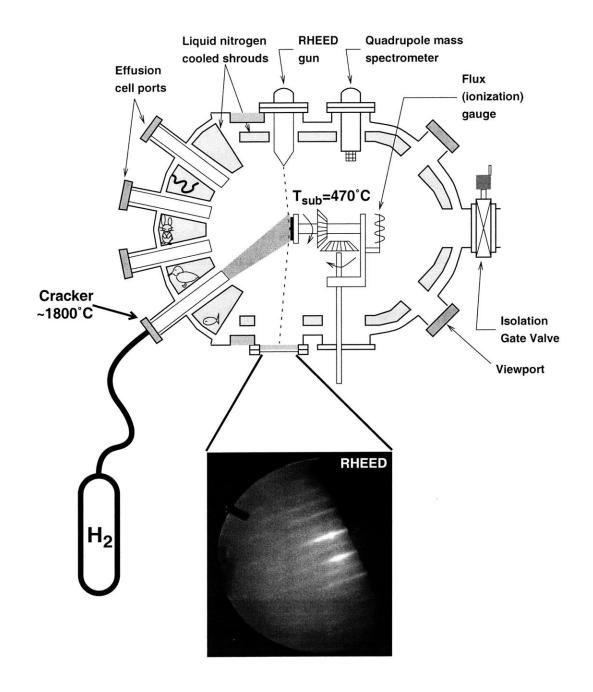

| 2.15 | A schematic view of the use of in situ atomic hydrogen in MBE                          |

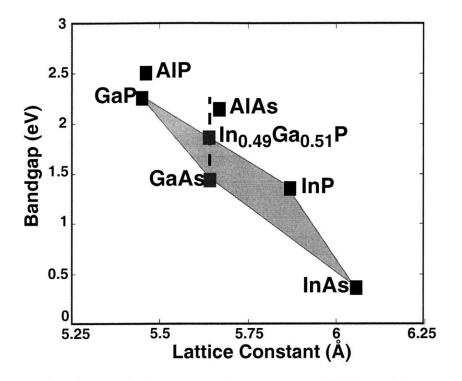

| 2.16 | Plot of bandgap vs. lattice constant of some common III-V materials                    |

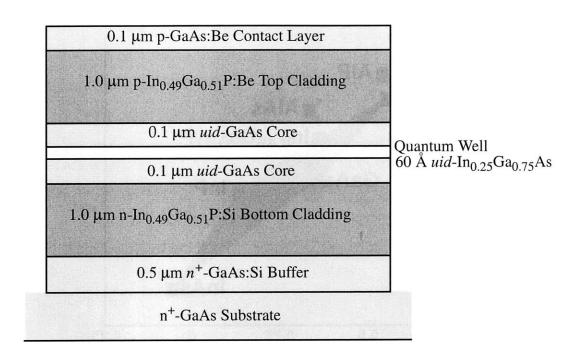

| 2.17 | InGaAs/GaAs/InGaP QW-SCH laser structure                                               |

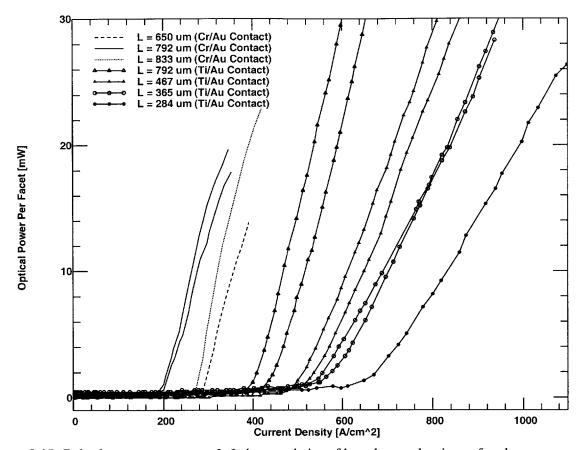

| 2.18 | Pulsed room temperature L-I characteristics of broad-area aluminum-free lasers         |

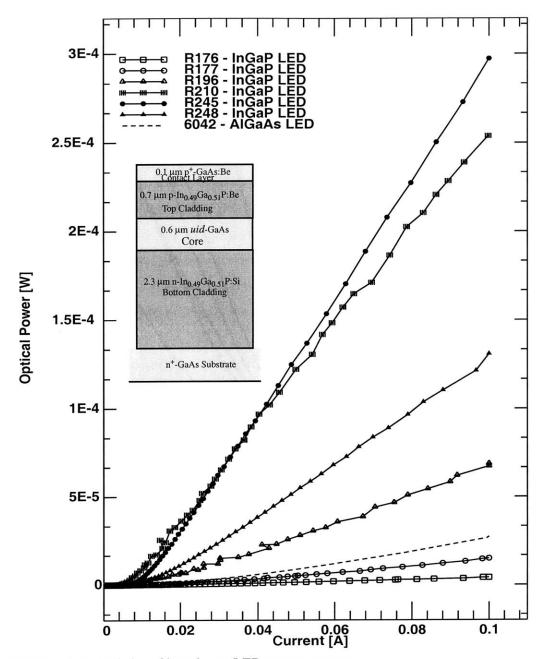

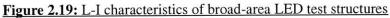

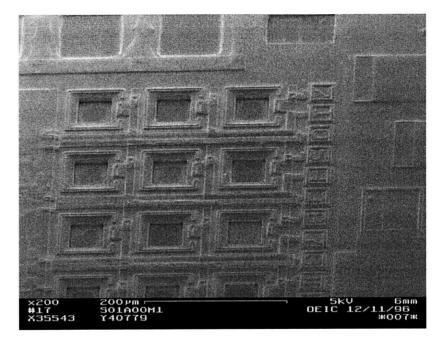

| 2.19 | L-I characteristics of broad-area LED test structures                                  |

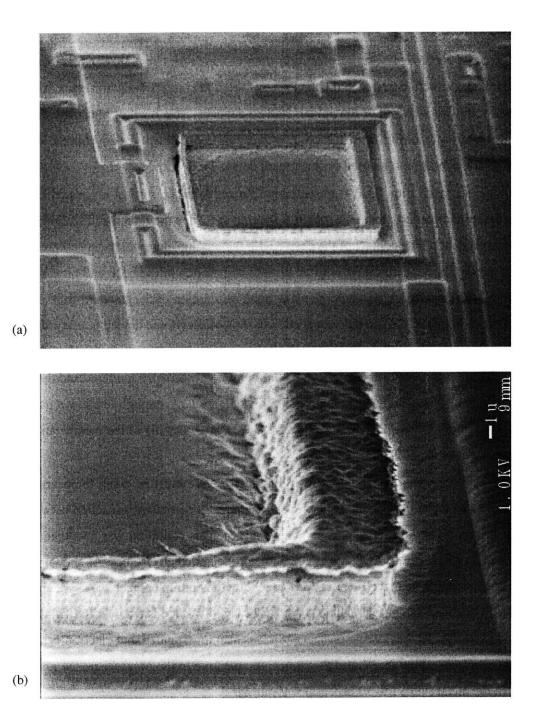

| 2.20 | SEM of OEIC surface and cross section showing post-growth polycrystalline deposits 76  |

| 2.21 | SEM of OEIC following dry etch of polycrystalline deposits                             |

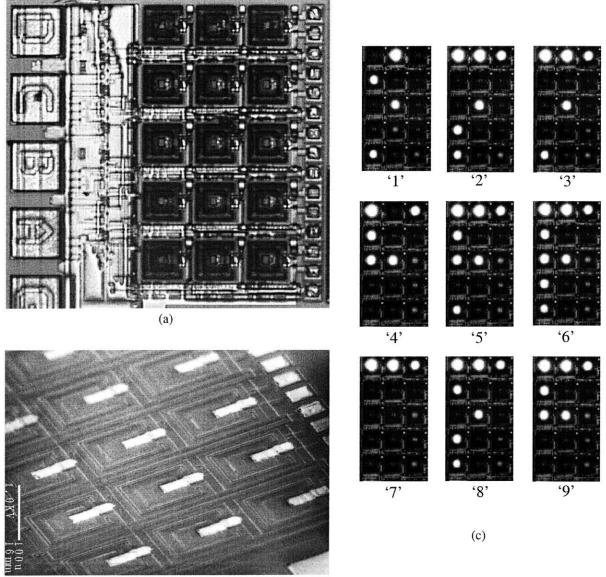

| 2.22 | First demonstration of integrated InGaP-based LEDs                                     |

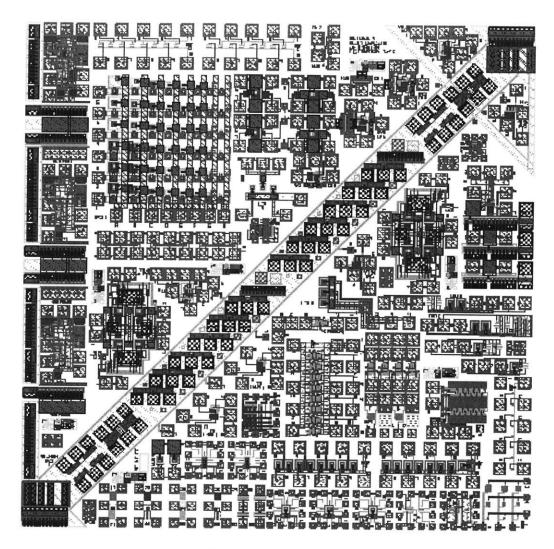

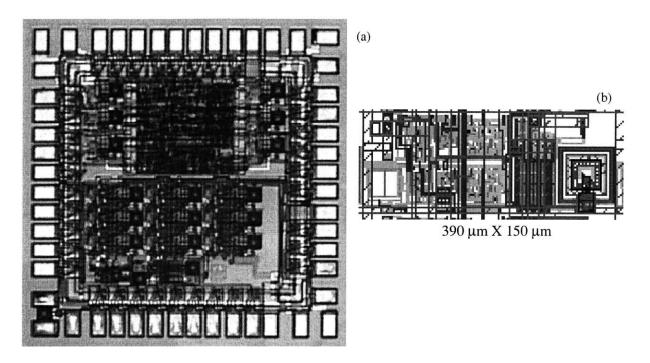

| 2.23 | Layout plot of the MIT-OEIC-4 test chip                                                |

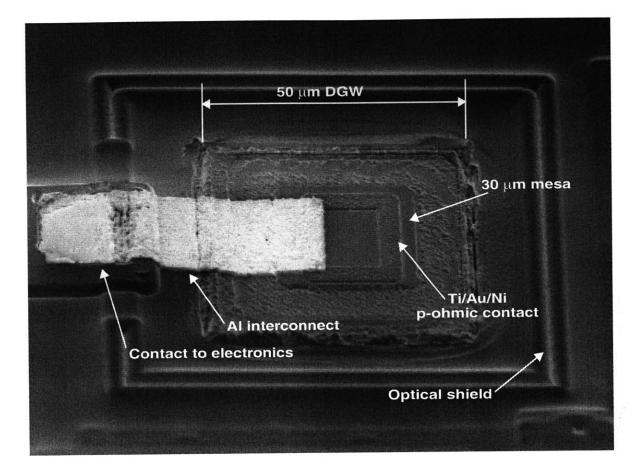

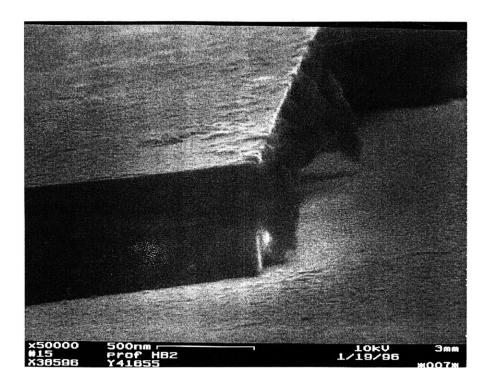

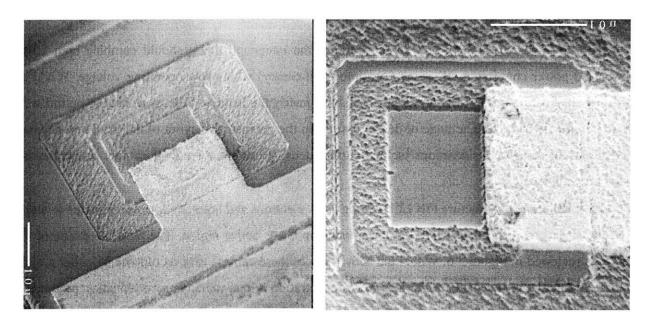

| 2.24 | SEM on an integrated LED                                                               |

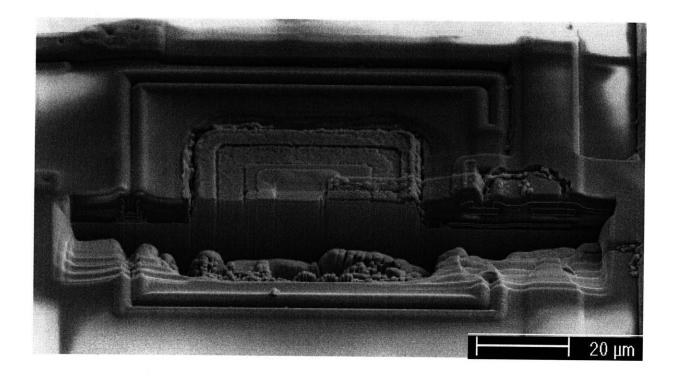

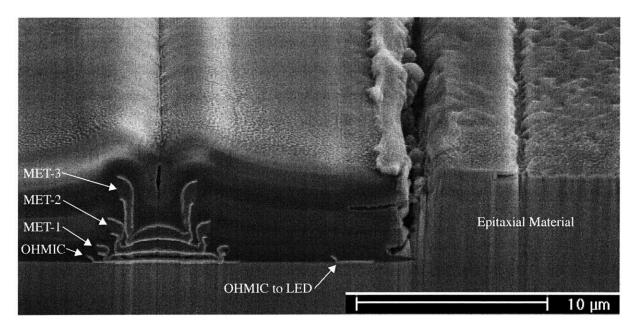

| 2.25 | FIBE cross section a completed LED                                            |

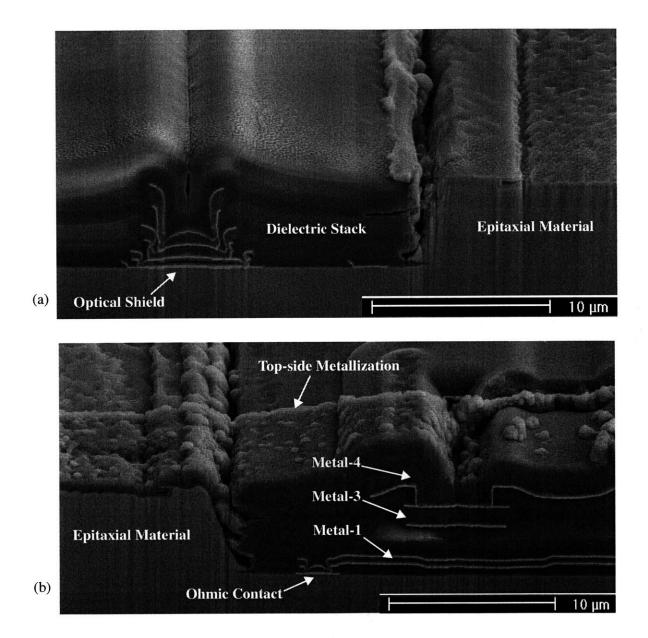

|------|-------------------------------------------------------------------------------|

| 2.26 | FIBE cross section of a completed LED; detailed views                         |

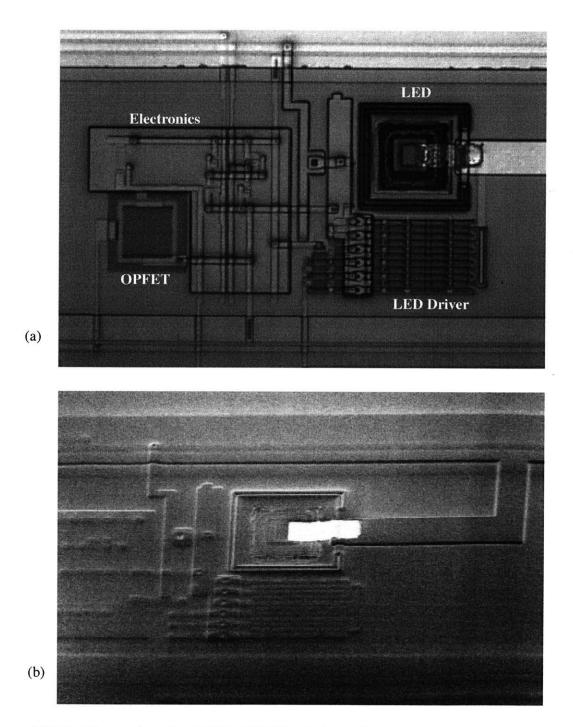

| 2.27 | EoE integration of and LED, OPFET, and electronics                            |

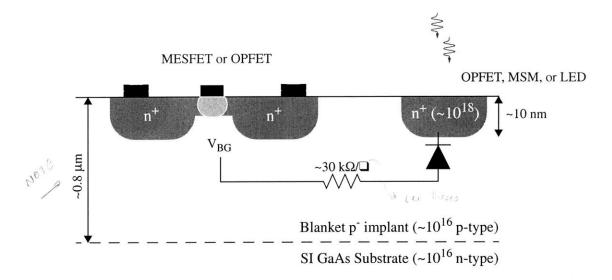

| 2.28 | Integrated LEDs, MSM photodetectors, and VLSI electronics                     |

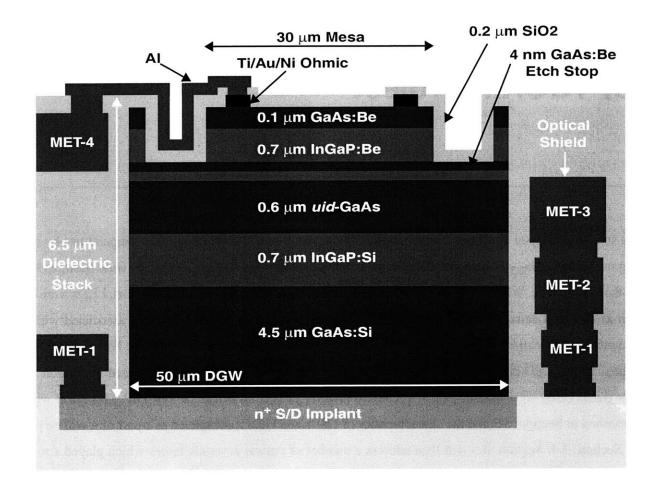

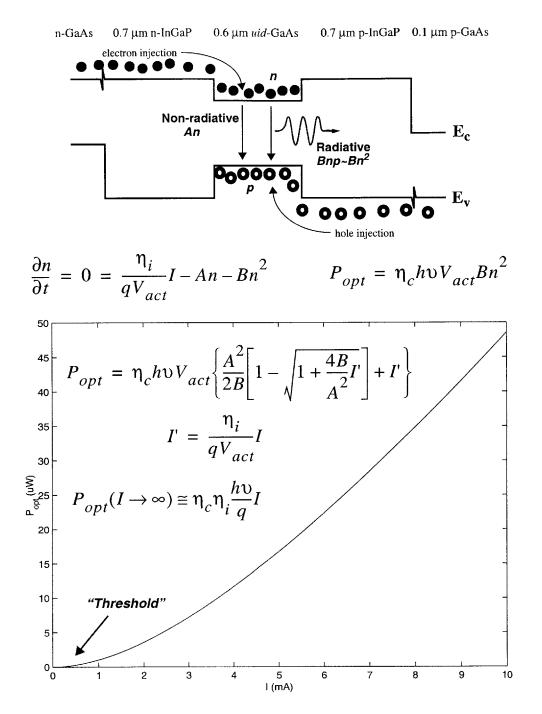

| 3.1  | Cross-sectional diagram of integrated LED structure                           |

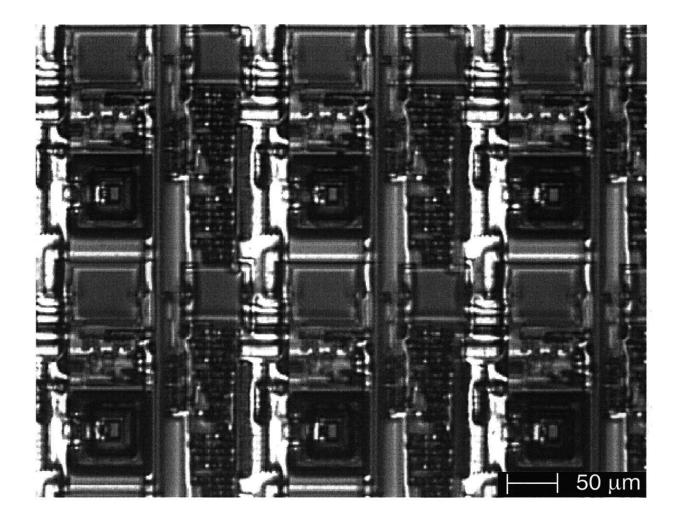

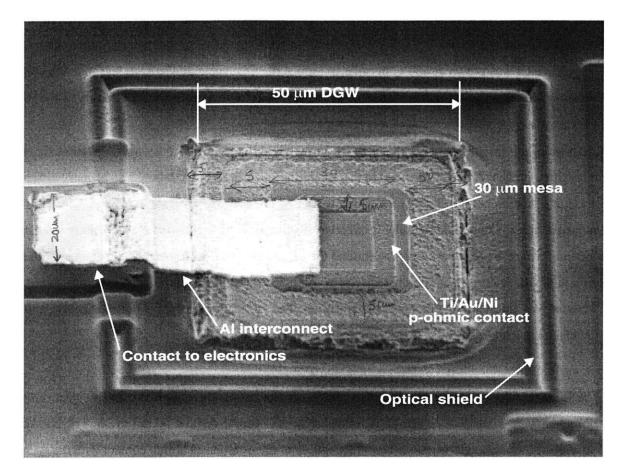

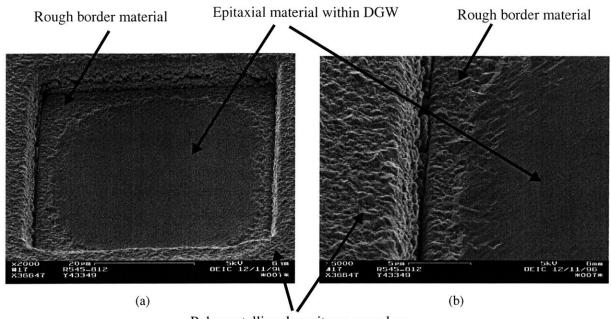

| 3.2  | SEM on an integrated LED                                                      |

| 3.3  | SEM of InGaP wet etching result                                               |

| 3.4  | SEM of LEDs on first OPTOCHIP OEIC showing poor interconnect metallization 92 |

| 3.5  | SEM of an integrated LED in an 85 µm DGW                                      |

| 3.6  | Basic LED operation                                                           |

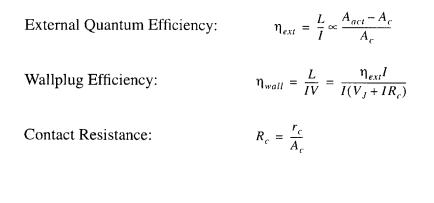

| 3.7  | Optimizing LED wallplug efficiency                                            |

| 3.8  | Emission pattern from LEDs made with various contact geometries               |

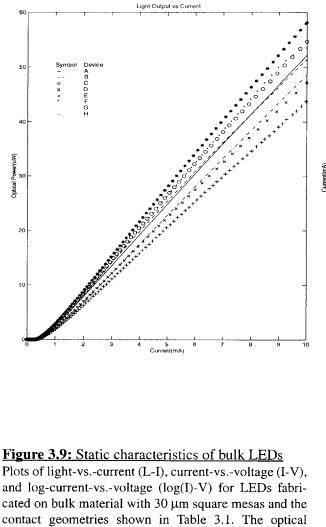

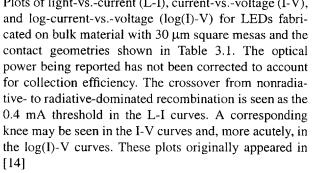

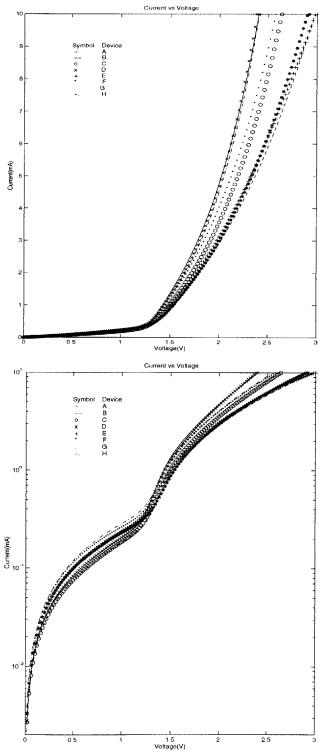

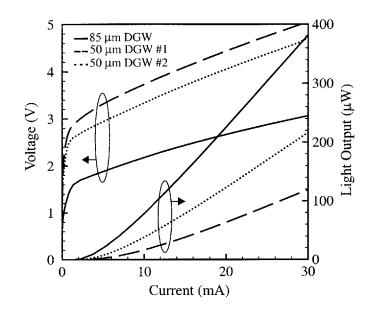

| 3.9  | Static characteristics of bulk LEDs                                           |

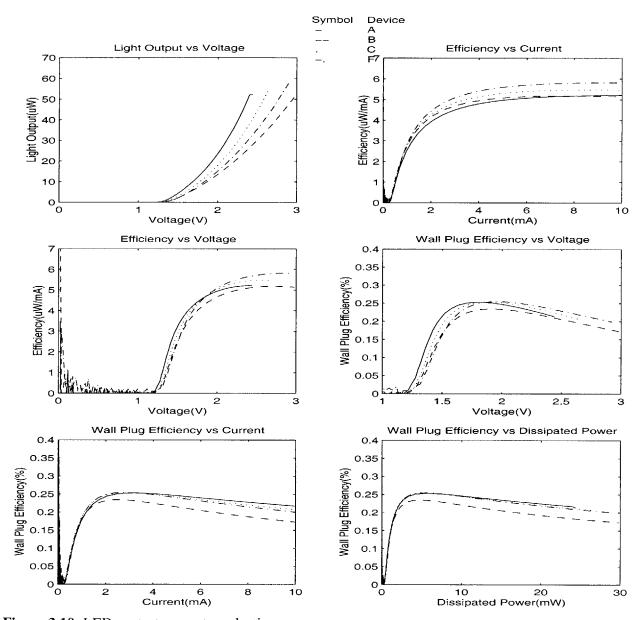

| 3.10 | LED contact geometry selection                                                |

| 3.11 | The OPTOCHIP project                                                          |

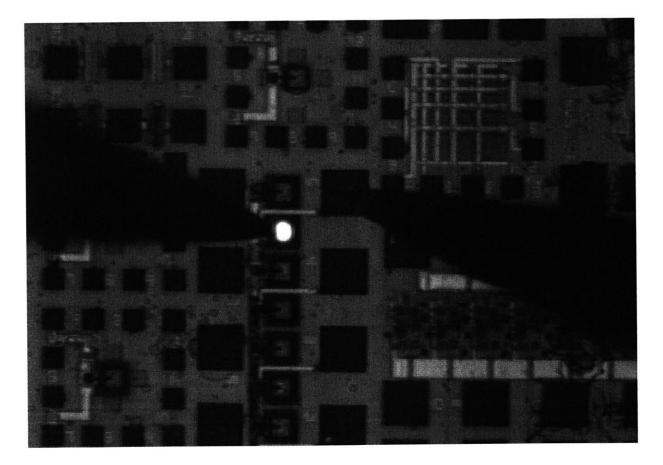

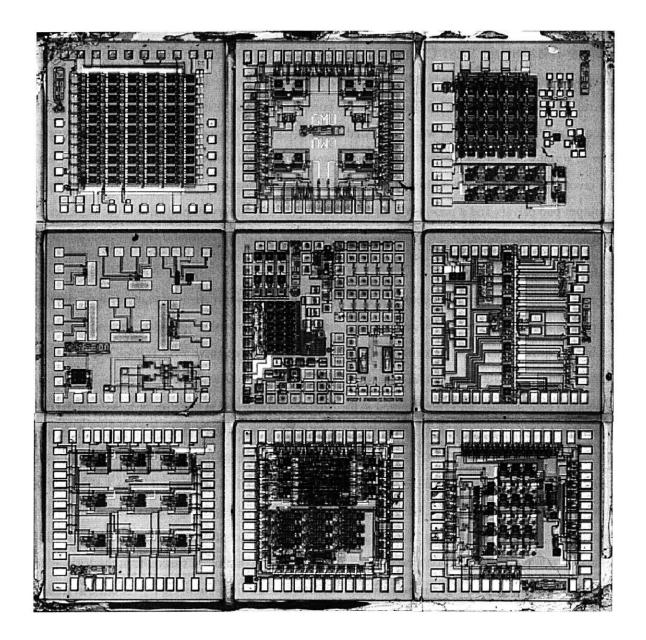

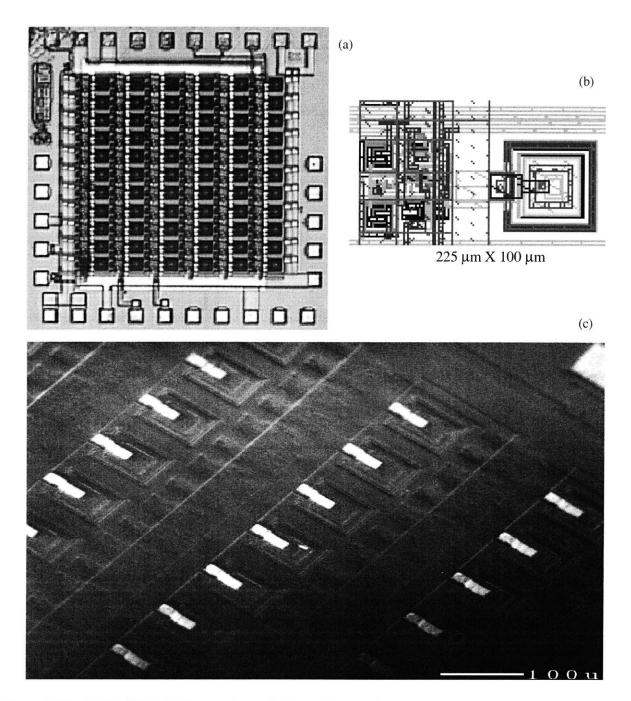

| 3.12 | Photograph of a finished OPTOCHIP master die                                  |

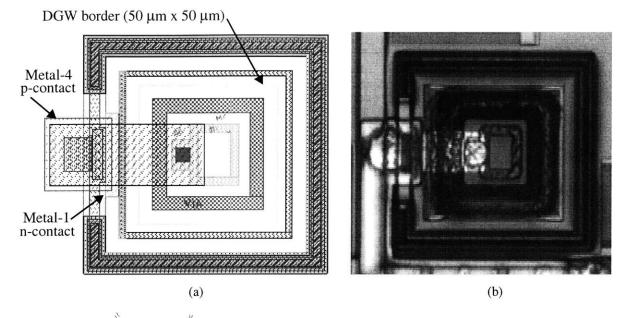

| 3.13 | LED drop in cell used in OPTOCHIP                                             |

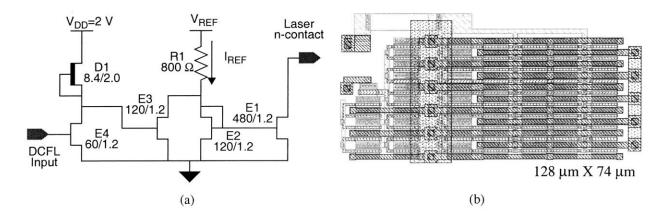

| 3.14 | LED driver drop in cell used in OPTOCHIP                                      |

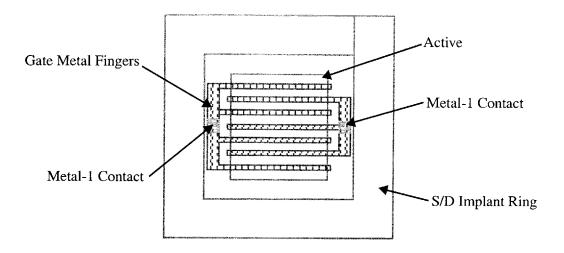

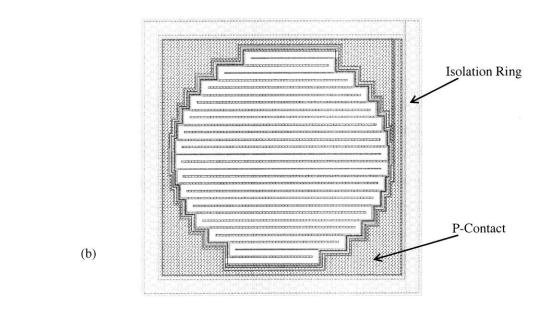

| 3.15 | Layout of an MSM photodetector drop-in cell used in OPTOCHIP                  |

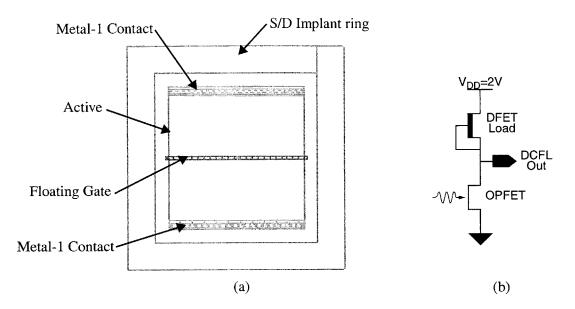

| 3.16 | Optically-sensitive FET (OPFET) drop-in cell used in OPTOCHIP                 |

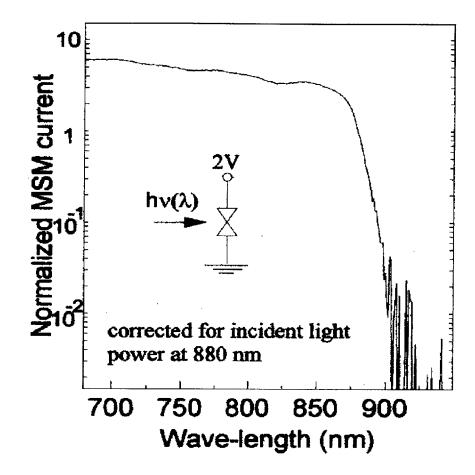

| 3.17 | GaAs photodetector optical responsivity spectrum                              |

| 3.18 | OPTOCHIP participants                                                         |

| 3.19 | OPTOCHIP OEIC example: optical neural network array                           |

| 3.20 | OPTOCHIP OEIC example: optical network interface                              |

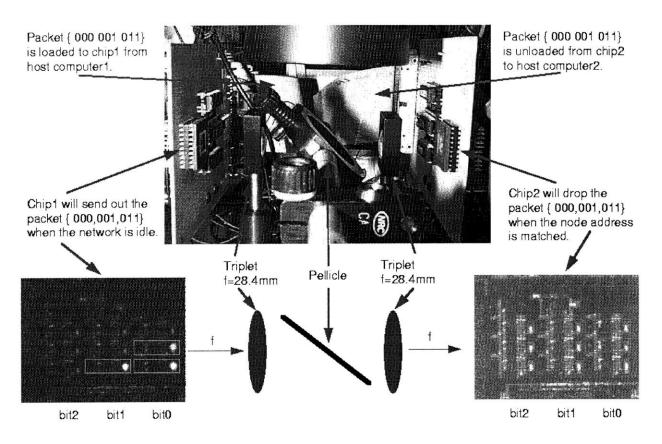

| 3.21 | Overview of the SAPIENT optical interconnect demonstration                    |

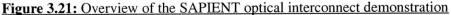

| 3.22 | Layout of the MIT OPTOCHIP design                                             |

| 3.23 | Poor material quality at perimeter of 50 µm DGWs                              |

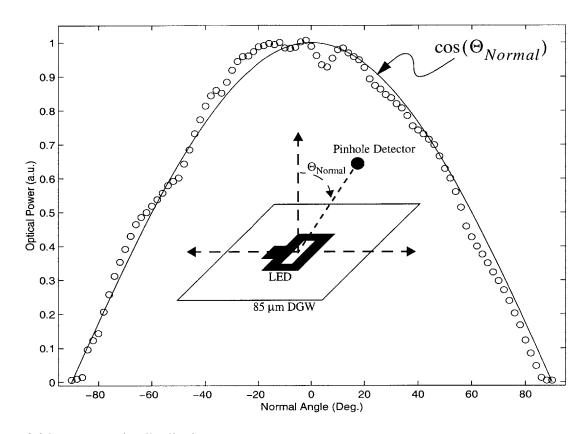

| 3.24 | LED angular distribution                                                      |

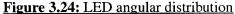

| 3.25 | Optical spectra of integrated LED emission                                    |

| 3.26 | Typical static characteristics of integrated LEDs on OPTOCHIP                 |

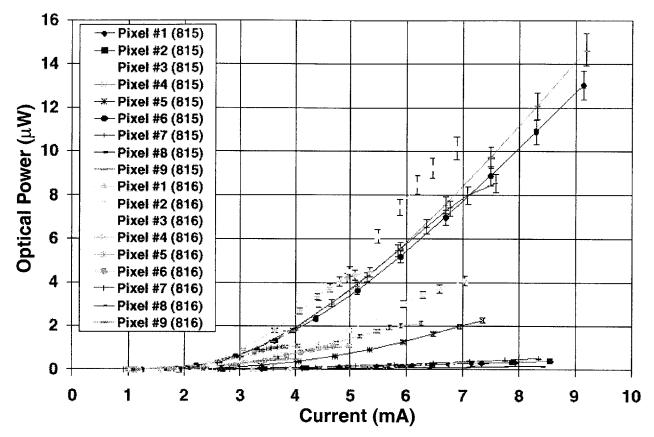

| 3.27 | Uniformity of OPTOCHIP LEDs                                                   |

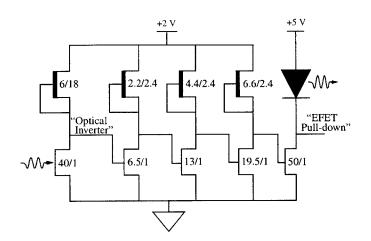

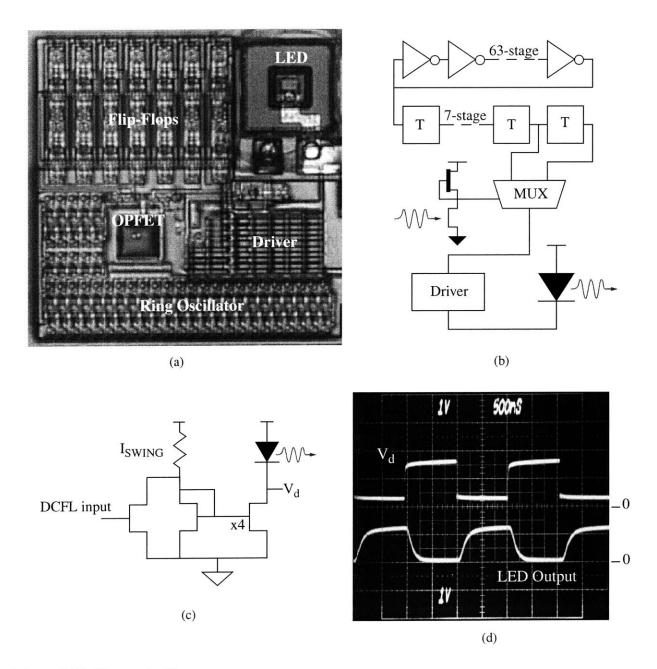

| 3.28 | "Basic Optoelectronic Circuit"                                                |

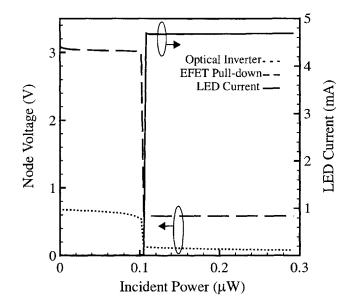

| 3.29 | Response of circuit shown in Figure 3.28 to an applied optical input          |

| 3.30 | "Number array"                                                                |

| 3.31 | "Smart pixel"                                                                 |

| 3.32 | FIBE cross section of an optical shield                                                       |

|------|-----------------------------------------------------------------------------------------------|

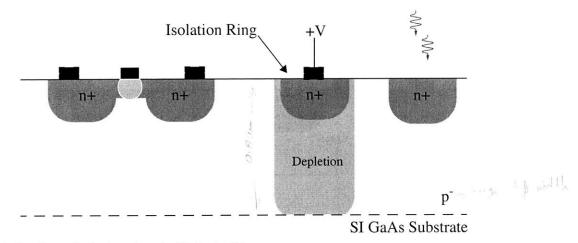

| 3.33 | H-GaAs III cross section showing mechanism for backgate crosstalk                             |

| 3.34 | Backgate isolation rings in H-GaAs III                                                        |

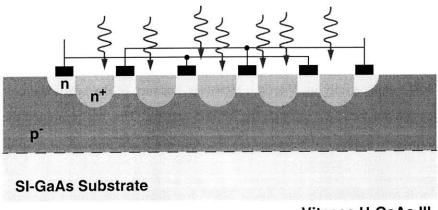

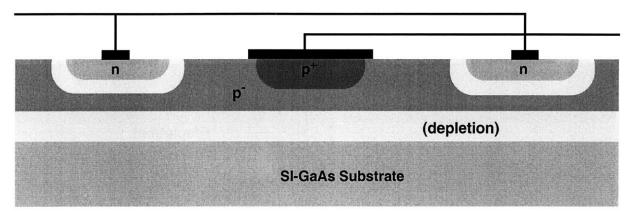

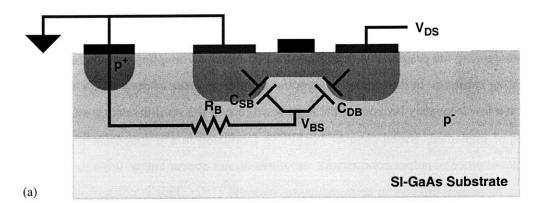

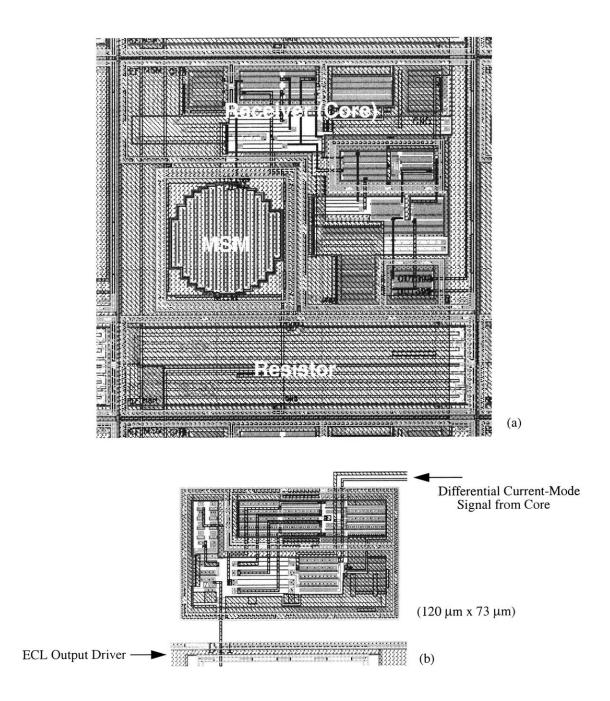

| 4.1  | Cross section of MSM photodetector made with standard Vitesse H-GaAs III process 132          |

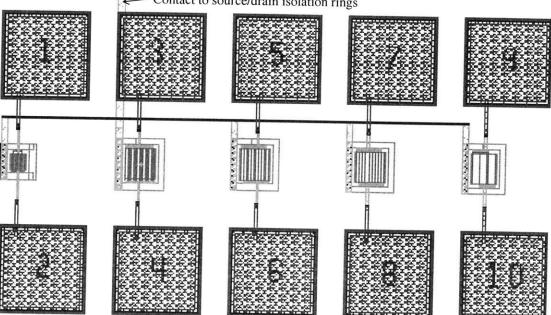

| 4.2  | Layout of test block from OPTOCHIP featuring various MSM photodetectors                       |

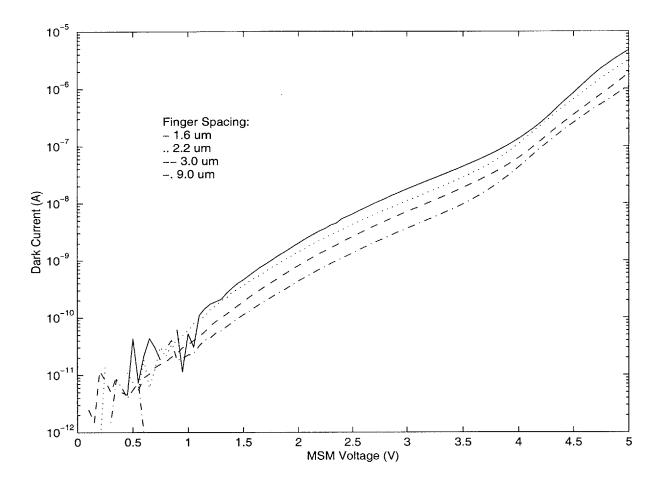

| 4.3  | Dark current of MSM photodetectors made with standard Vitesse H-GaAs III process 134          |

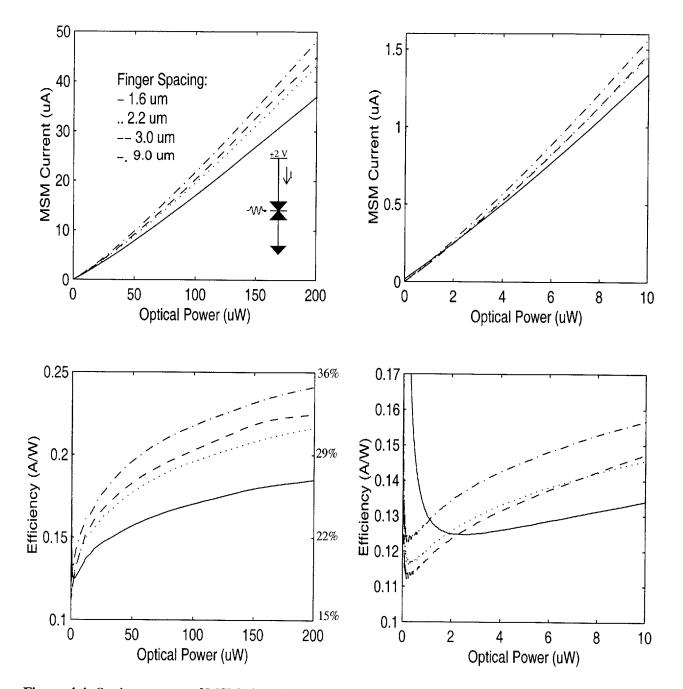

| 4.4  | Static response of MSM photodetectors made with standard Vitesse H-GaAs III process 135       |

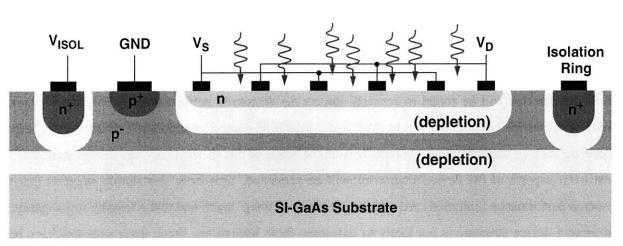

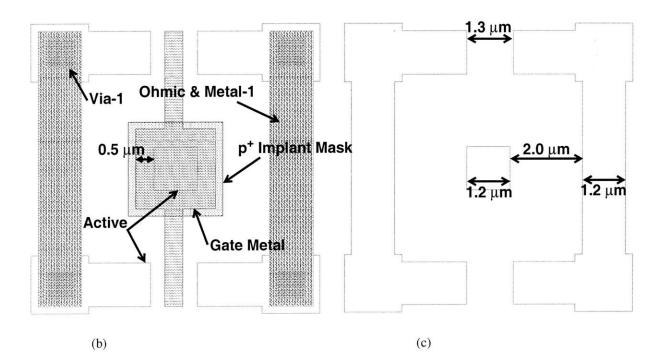

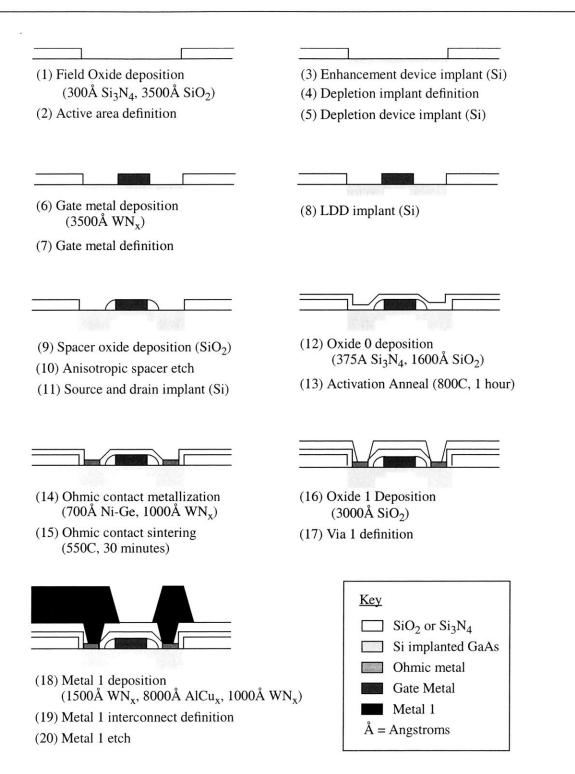

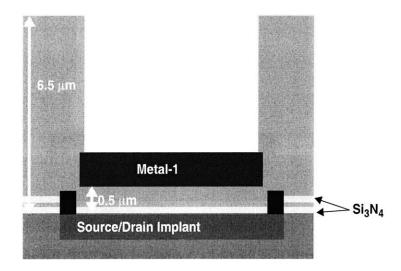

| 4.5  | Cross section and layout of modified MSM photodetector in the Vitesse H-GaAs IV process . 138 |

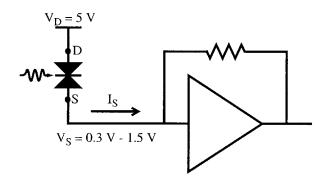

| 4.6  | Common biasing configuration of MSM photodetectors in an integrated receiver                  |

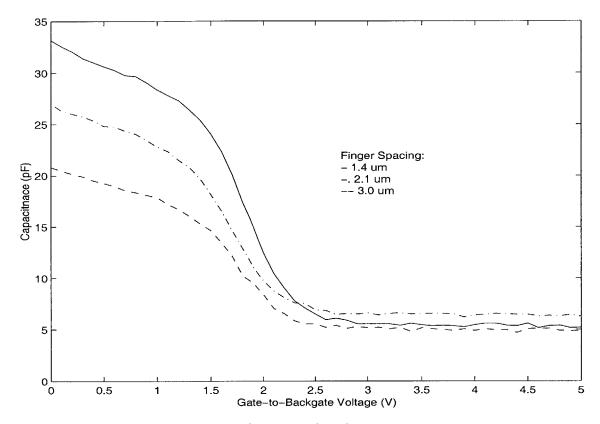

| 4.7  | Capacitance vs. voltage of modified MSM photodetectors                                        |

| 4.8  | Dark current of MSM27                                                                         |

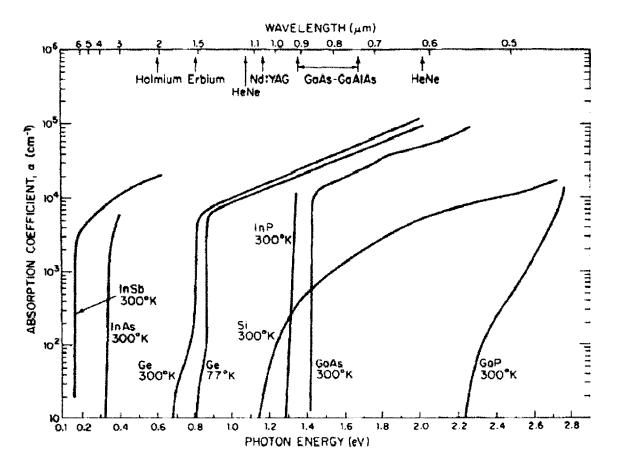

| 4.9  | Optical absorption coefficients of various semiconductors                                     |

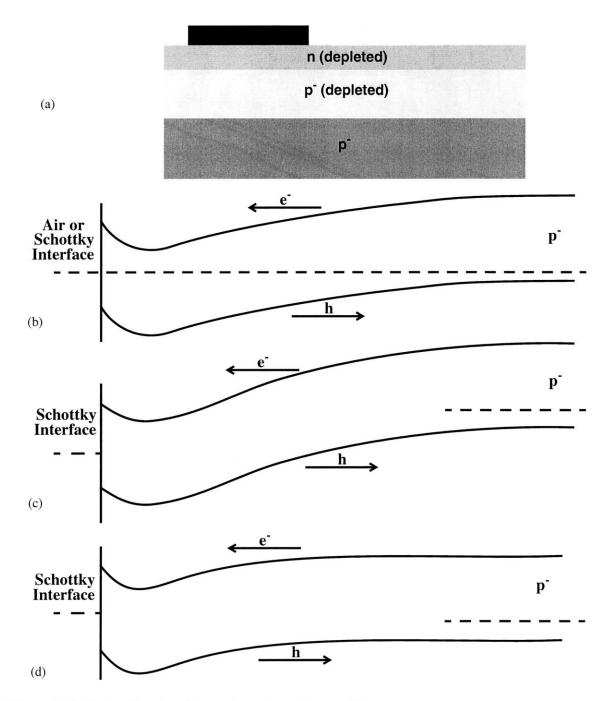

| 4.10 | Vertical band profiles under various bias conditions                                          |

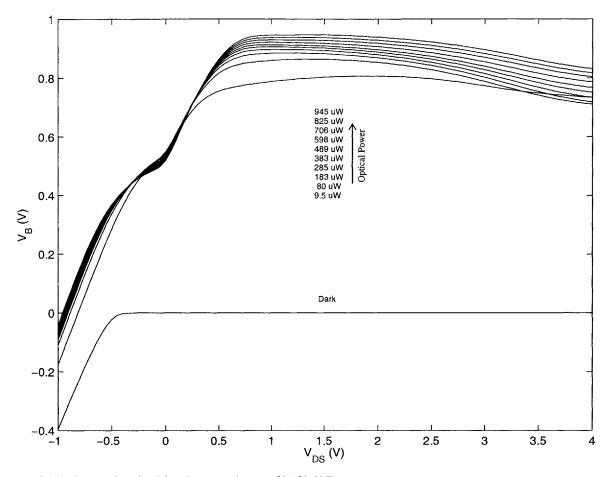

| 4.11 | Open-circuited backgate voltage of MSM27                                                      |

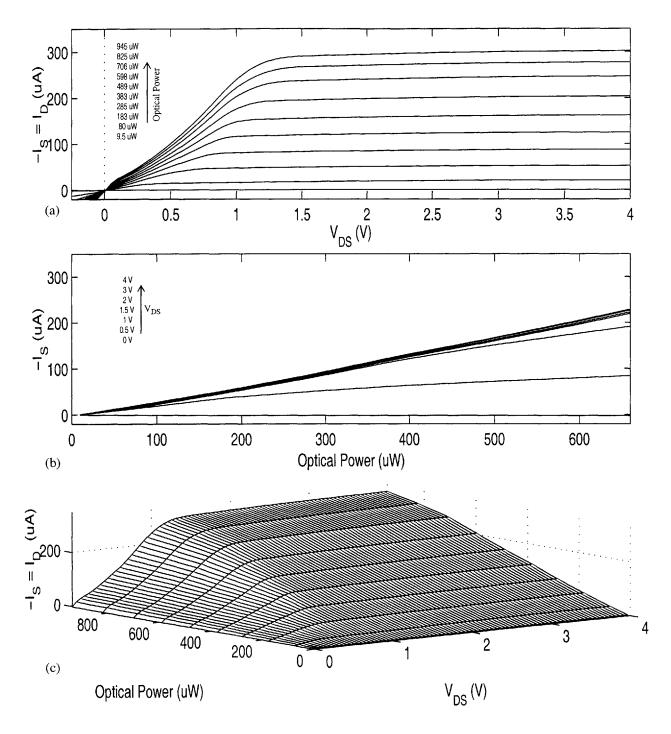

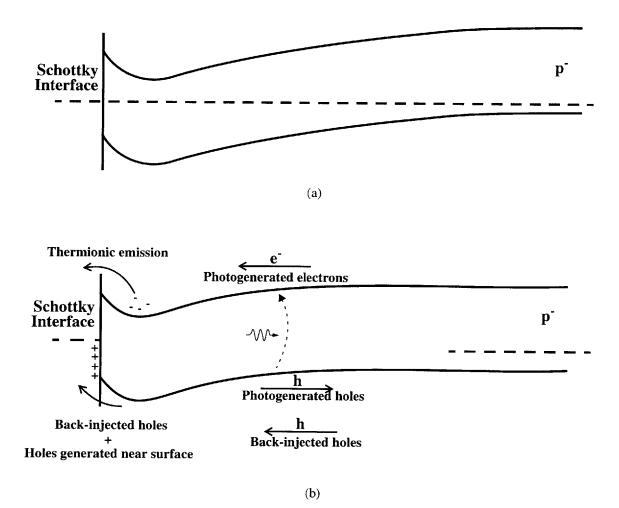

| 4.12 | Static MSM27 photocurrent with backgate open-circuited                                        |

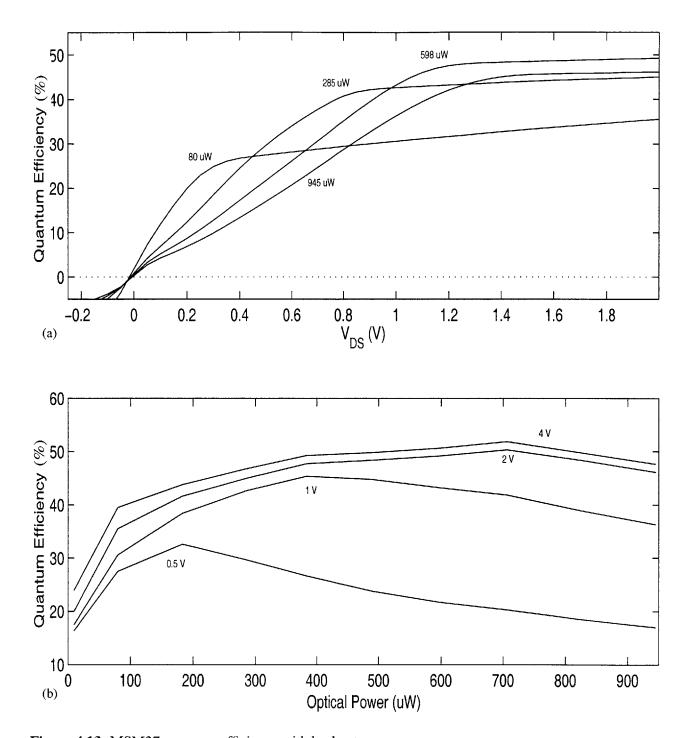

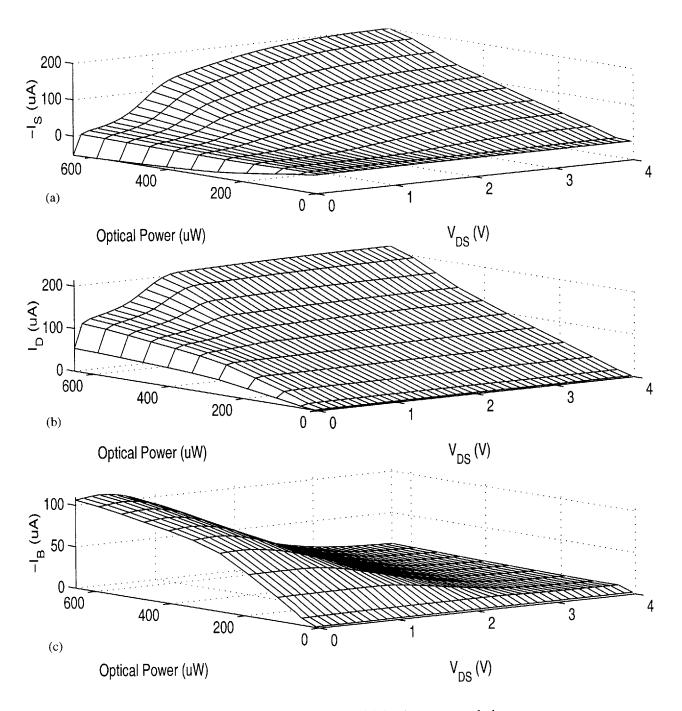

| 4.13 | MSM27 quantum efficiency with backgate open                                                   |

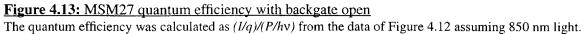

| 4.14 | Biasing mechanism for the source and drain Schottky diodes                                    |

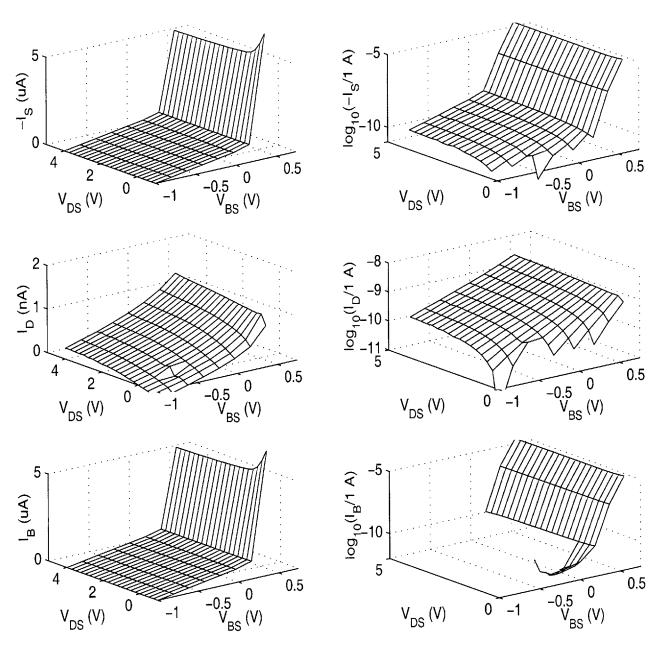

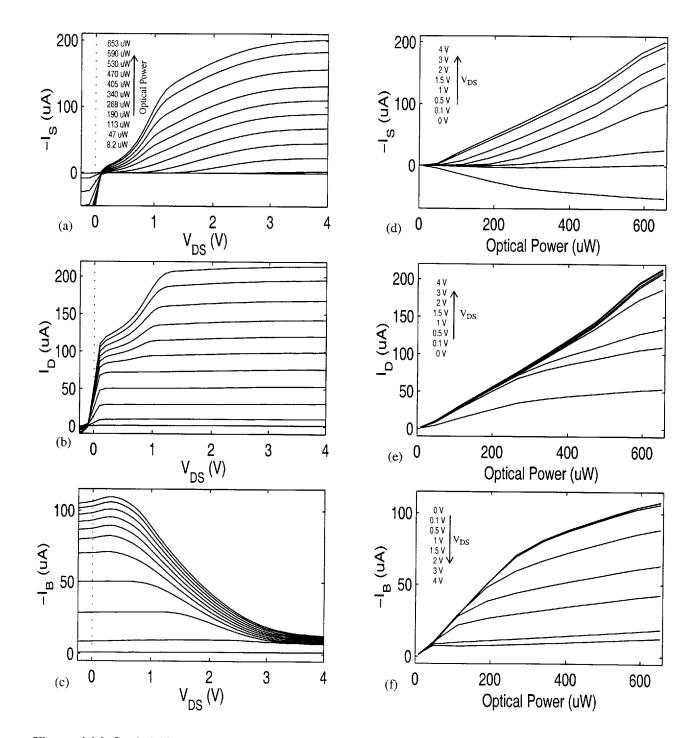

| 4.15 | Overview of static MSM27 photocurrent with backgate grounded                                  |

| 4.16 | Static MSM27 photocurrent with backgate grounded                                              |

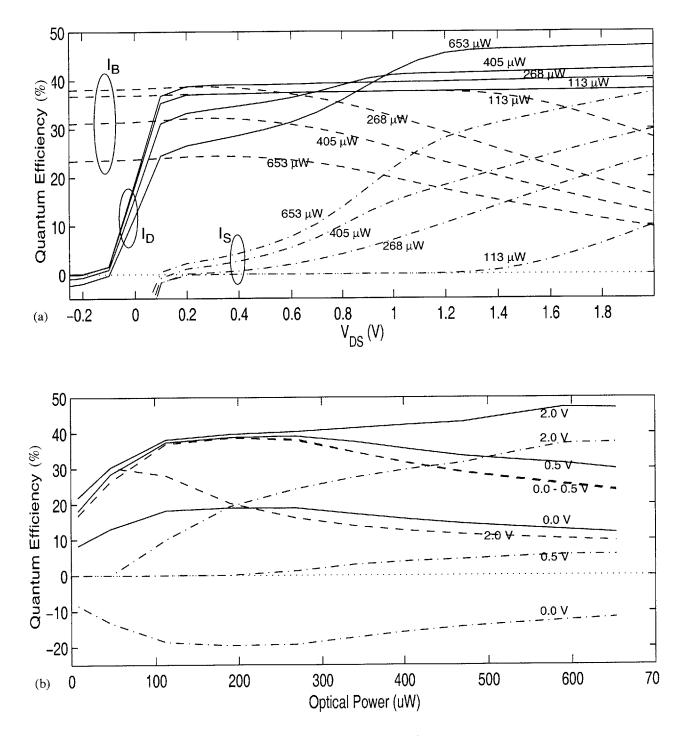

| 4.17 | MSM27 quantum efficiency with backgate grounded                                               |

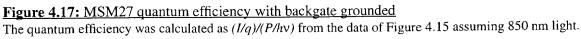

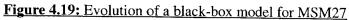

| 4.18 | Comparison of devices with varying active areas                                               |

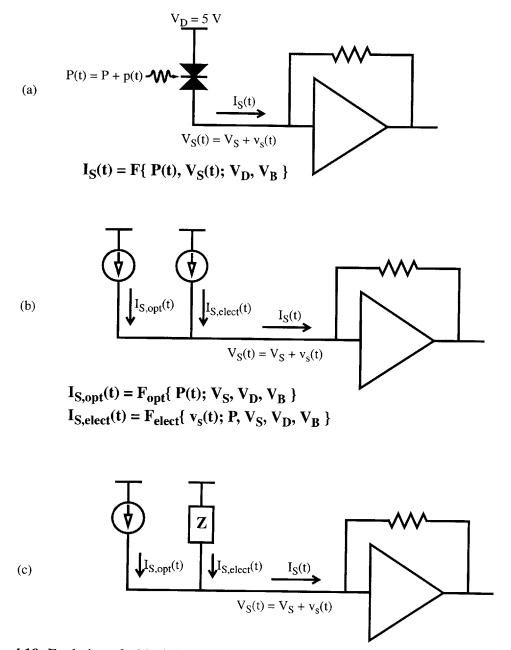

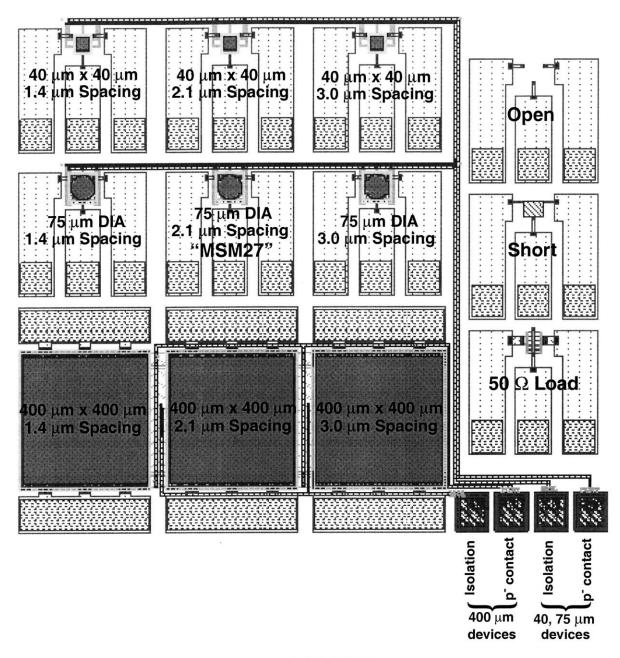

| 4.19 | Evolution of a black-box model for MSM27                                                      |

| 4.20 | Layout of detector test structures on MIT-OEIC-7                                              |

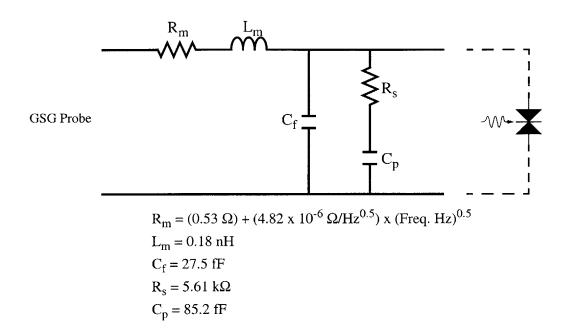

| 4.21 | Equivalent circuit for ground-signal-ground pads seen in Figure 4.20                          |

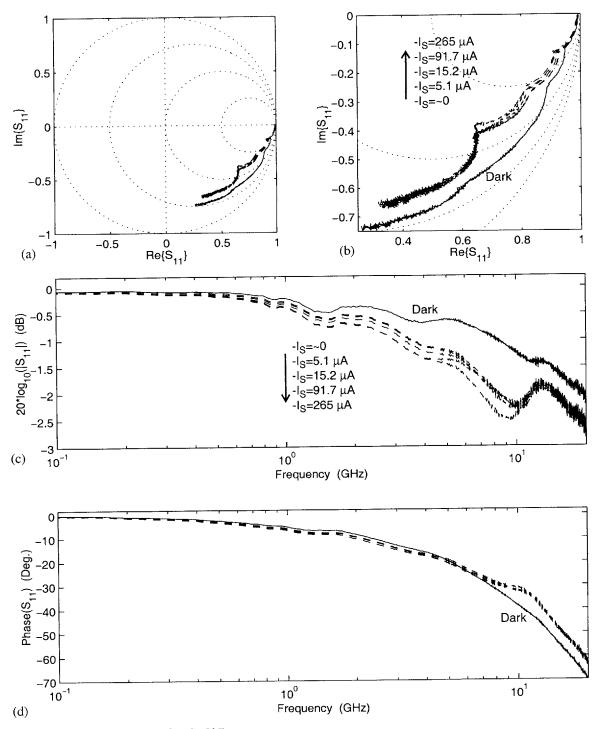

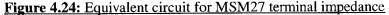

| 4.22 | Measured S <sub>11</sub> of MSM27                                                             |

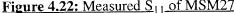

| 4.23 | Terminal admittance of MSM27                                                                  |

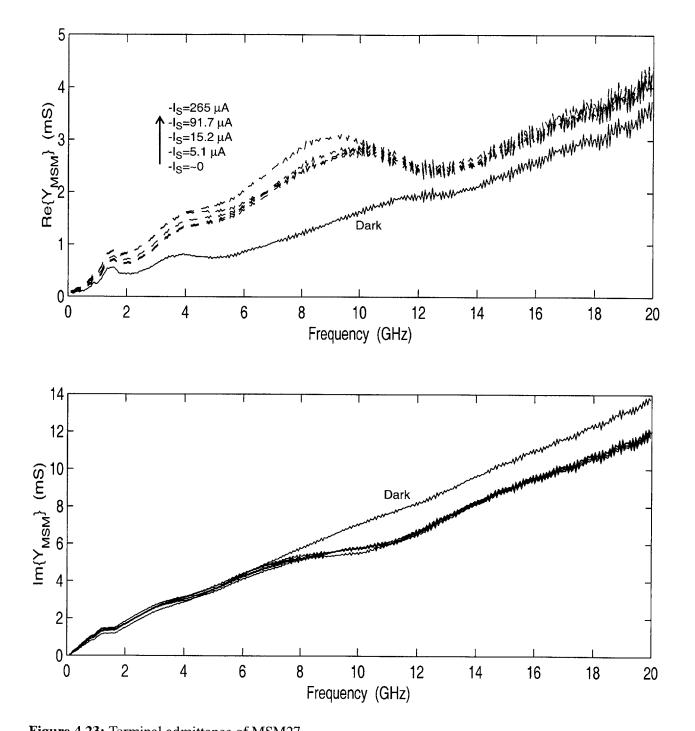

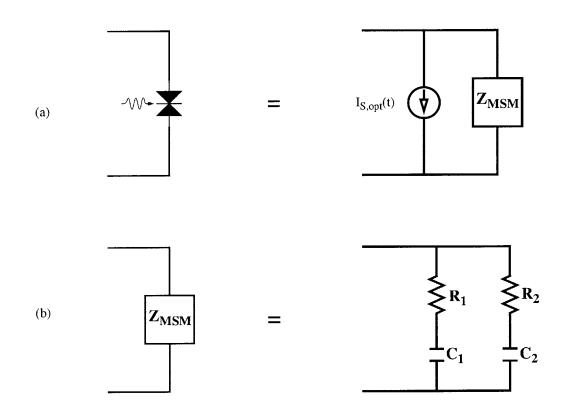

| 4.24 | Equivalent circuit for MSM27 terminal impedance                                               |

| 4.25 | Comparison of measured and modeled $S_{11}$ of MSM27                                          |

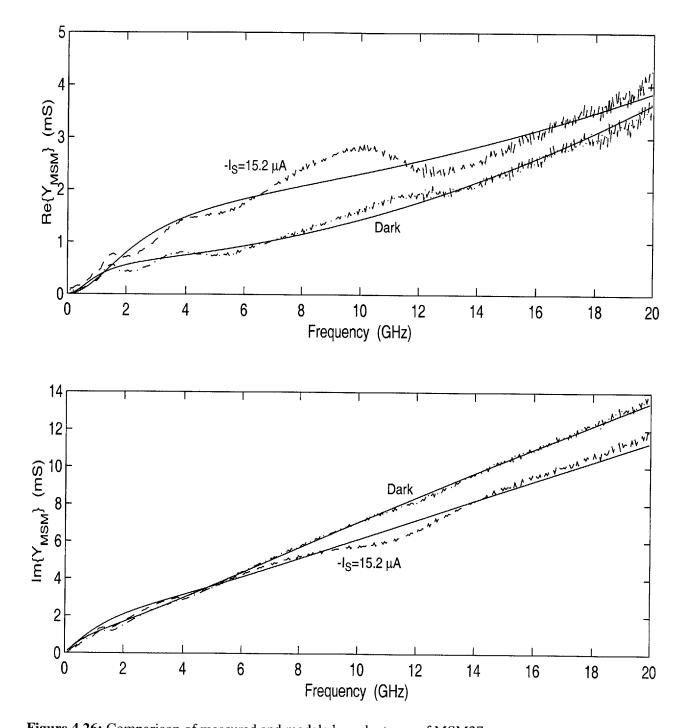

| 4.26 | Comparison of measured and modeled conductance of MSM27                                       |

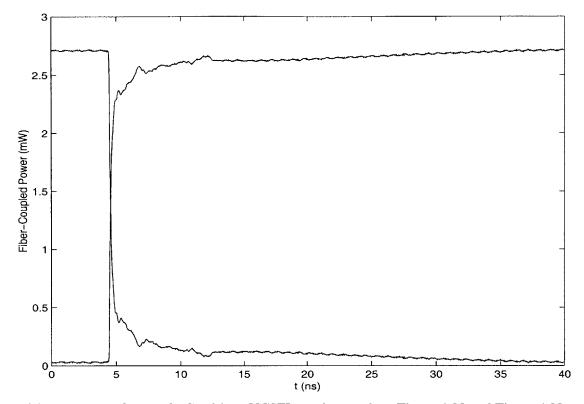

| 4.27 | Step waveforms of ECL-driven VCSEL used to produce Figure 4.28 and Figure 4.29 169            |

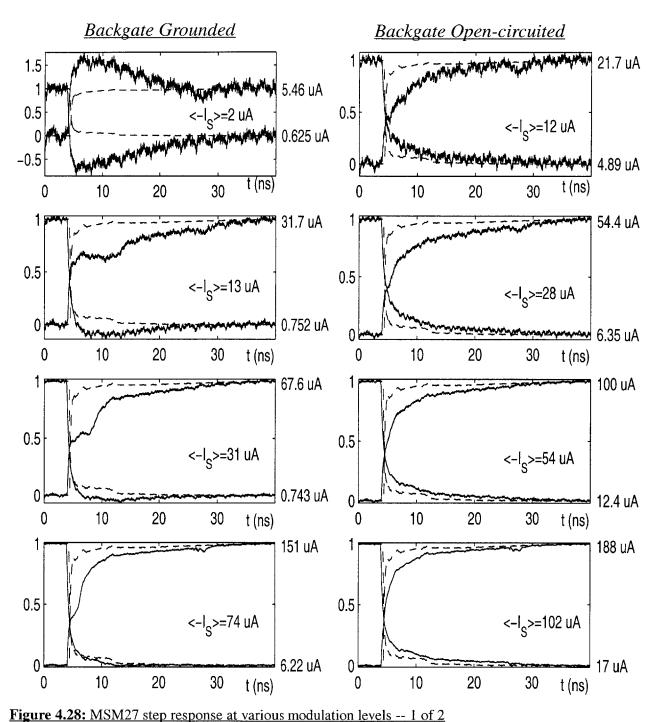

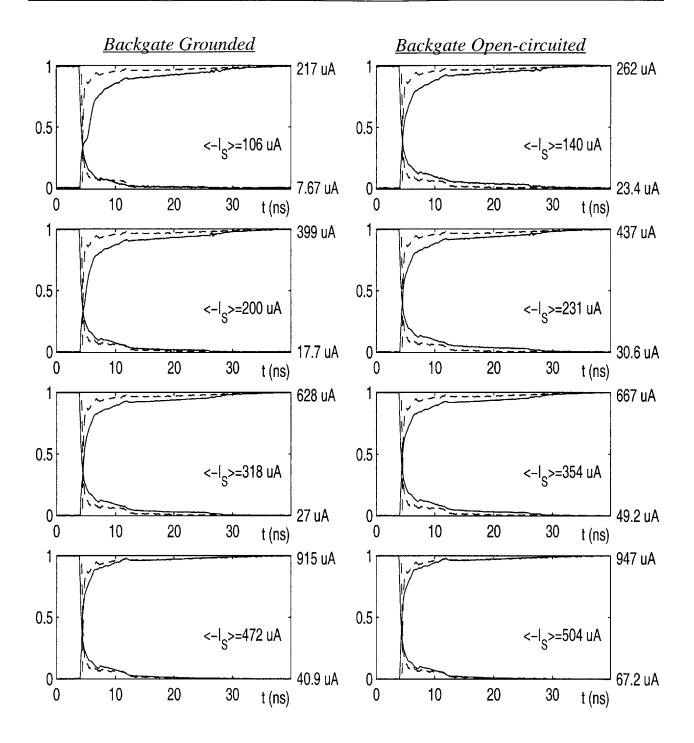

| 4.28 | MSM27 step response at various modulation levels 1 of 2                                       |

| 4.29 | MSM27 step response at various modulation levels 2 of 2                                       |

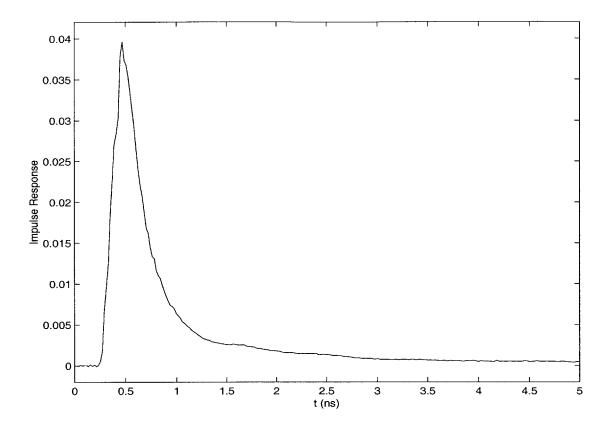

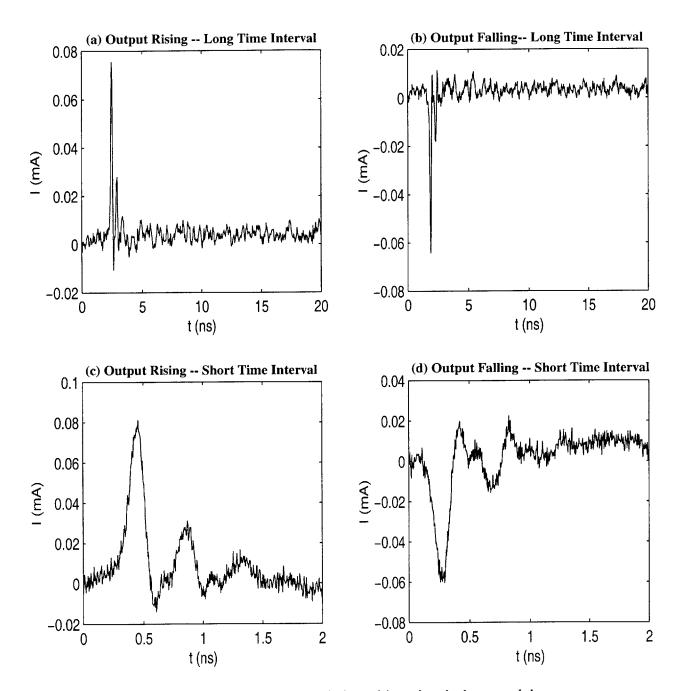

| 4.30 | MSM27 impulse response                                                                        |

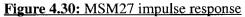

| 4.31 | Linear-system model of MSM27 photocurrent at high optical power levels                        |

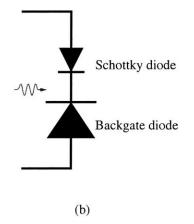

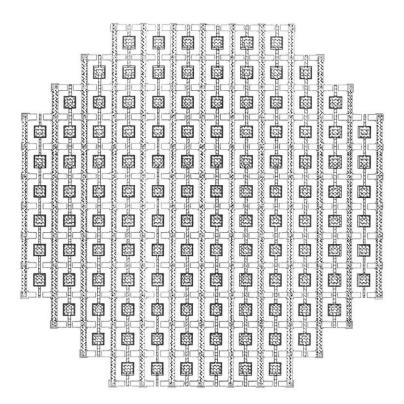

| 4.32 | Modification of MSM-like structure to use backgate diode as photodetector                     |

|      |                                                                                               |

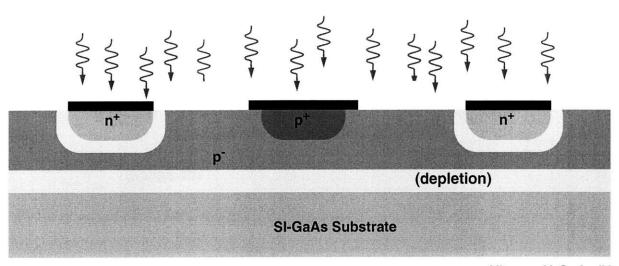

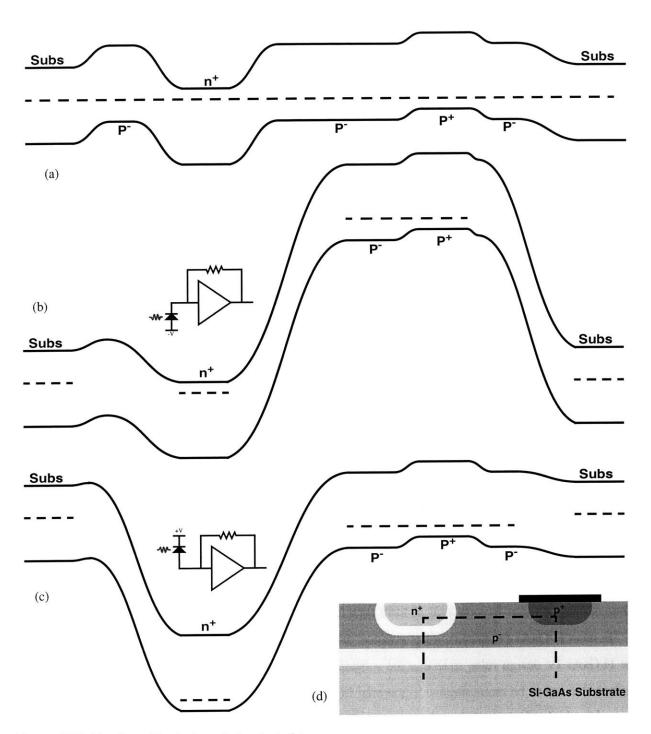

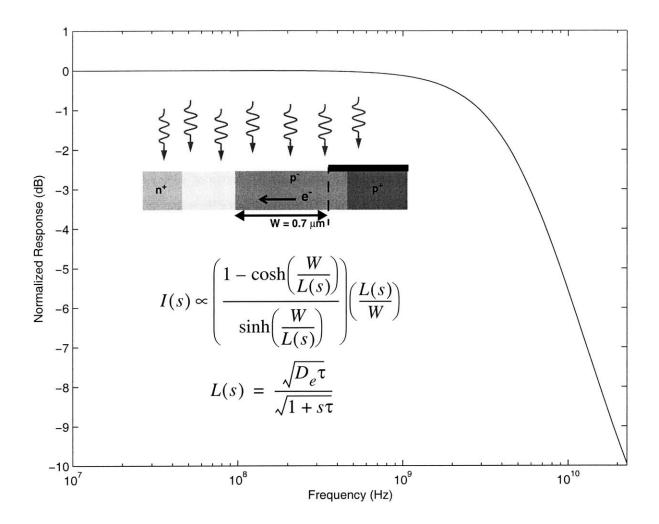

| 4.33 | Lateral pin photodiode in the standard Vitesse H-GaAs IV process                        |

|------|-----------------------------------------------------------------------------------------|

| 4.34 | 75 µm diameter lateral pin photodetector                                                |

| 4.35 | Band profiles in lateral pin photodetector                                              |

| 4.36 | Frequency response of photogenerated carrier diffusion in lateral pin photodetector 182 |

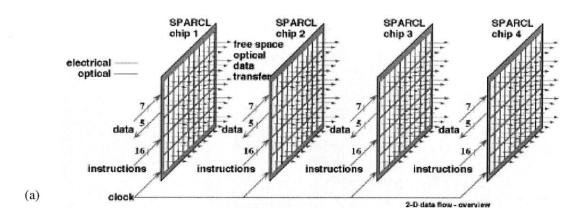

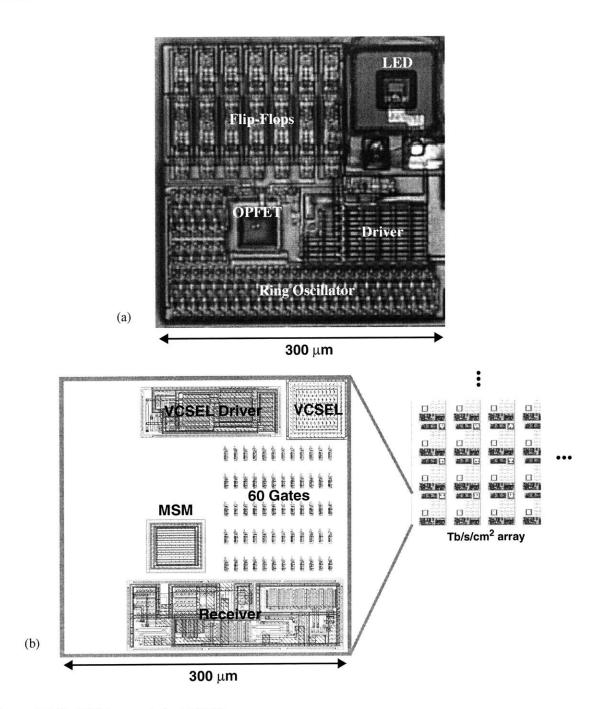

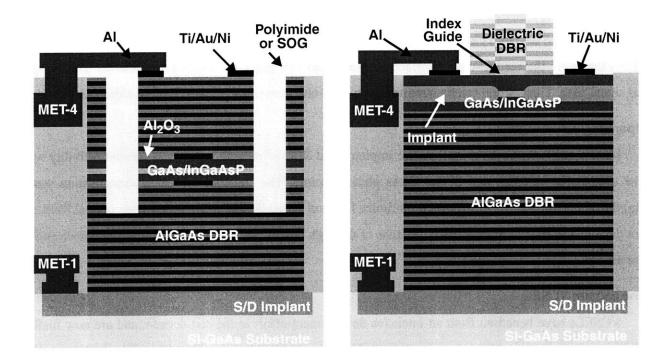

| 5.1  | EoE Tb/s smart pixel OEICs                                                              |

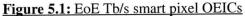

| 5.2  | EoE parallel fiber-optic data link OEICs                                                |

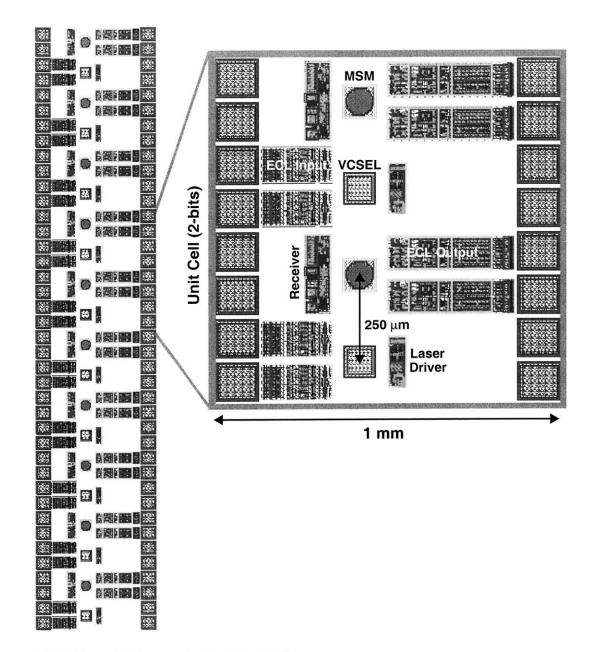

| 5.3  | Possible integrated VCSEL structures                                                    |

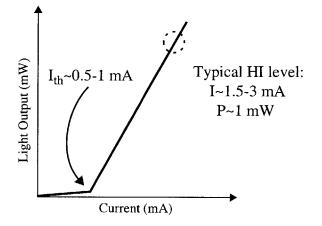

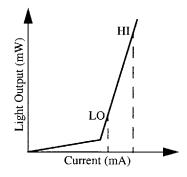

| 5.4  | L-I characteristics of a VCSEL                                                          |

| 5.5  | Comparison of communication links and digital interconnects                             |

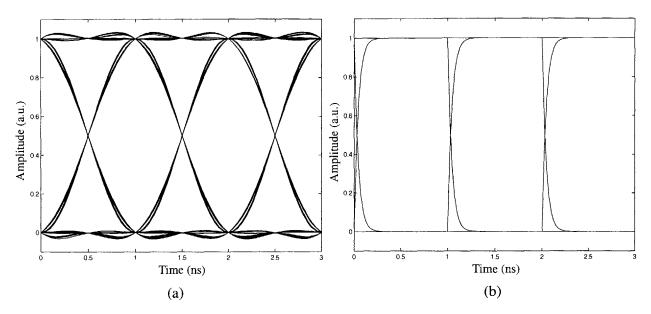

| 5.6  | Simulated eye diagrams                                                                  |

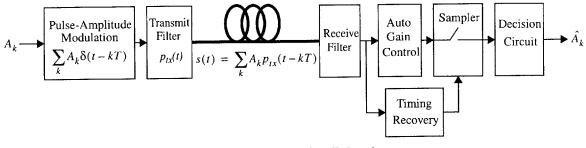

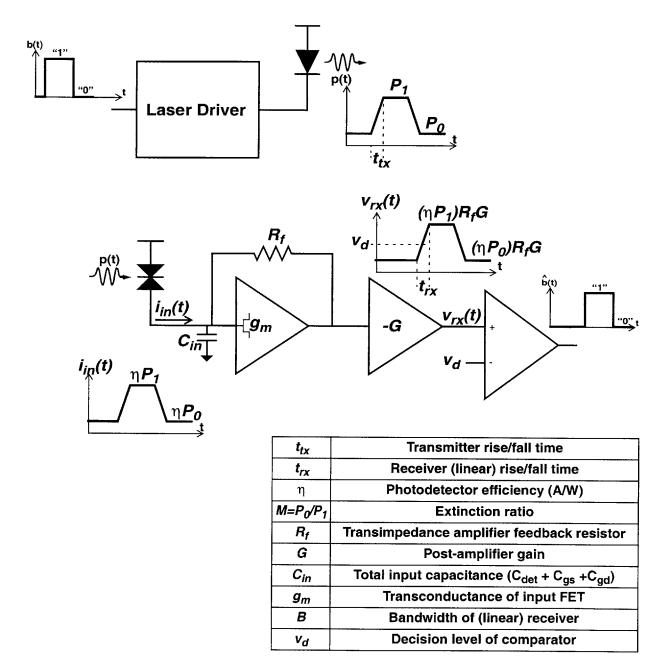

| 5.7  | Anatomy of a digital optical interconnect                                               |

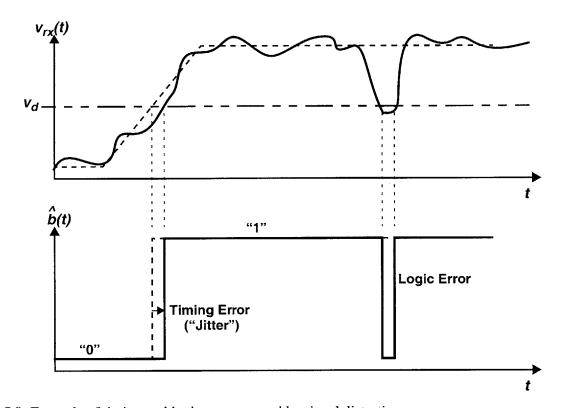

| 5.8  | Example of timing and logic errors caused by signal distortion                          |

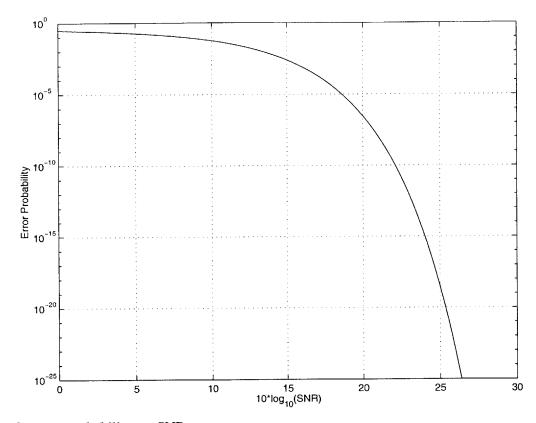

| 5.9  | Error probability vs. SNR                                                               |

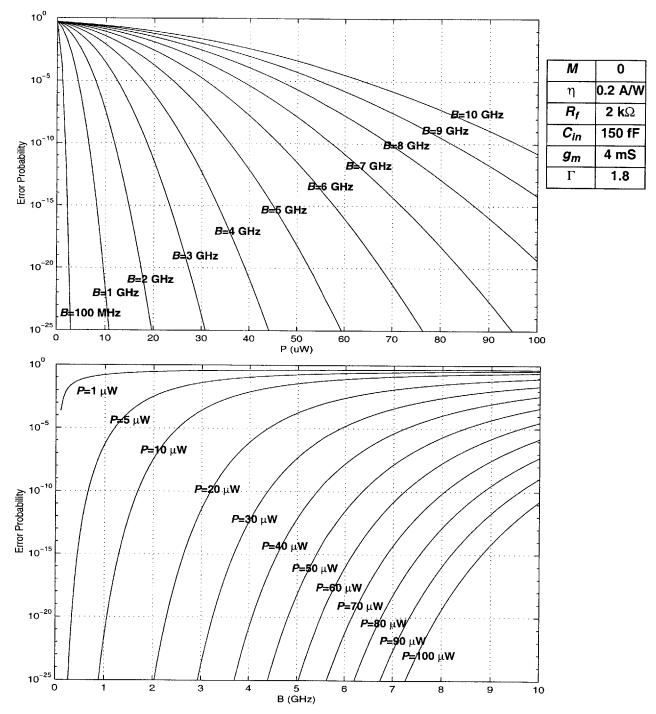

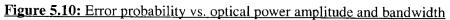

| 5.10 | Error probability vs. optical power amplitude and bandwidth                             |

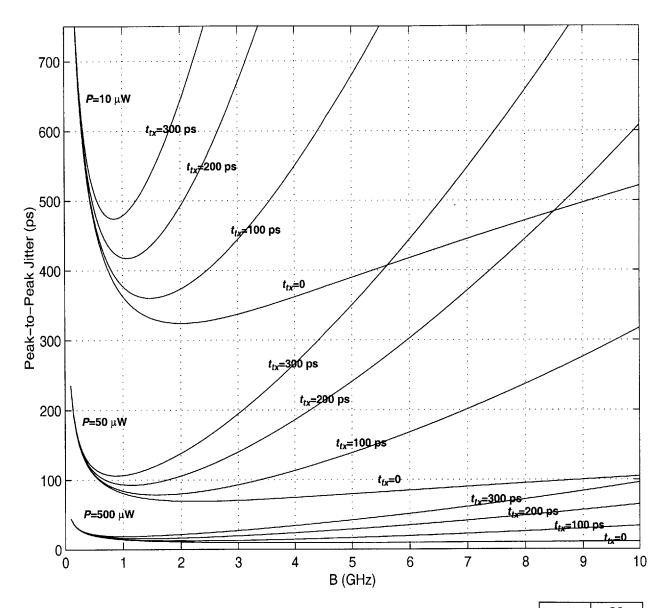

| 5.11 | Jitter vs. bandwidth                                                                    |

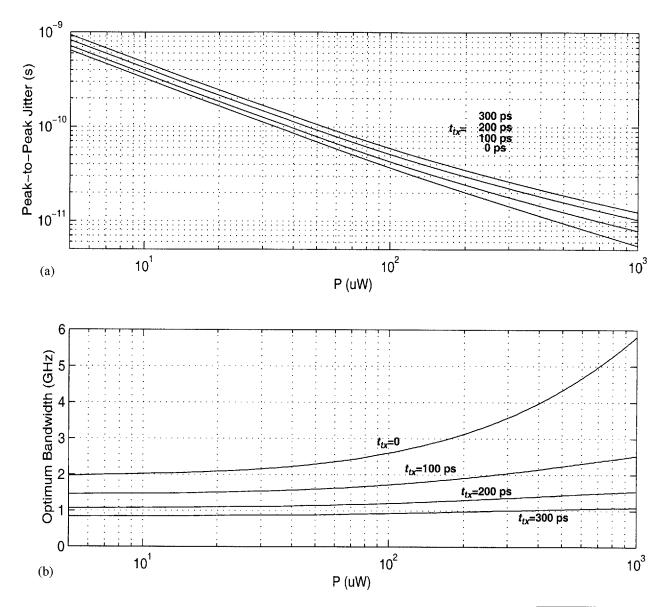

| 5.12 | Jitter vs. optical power amplitude                                                      |

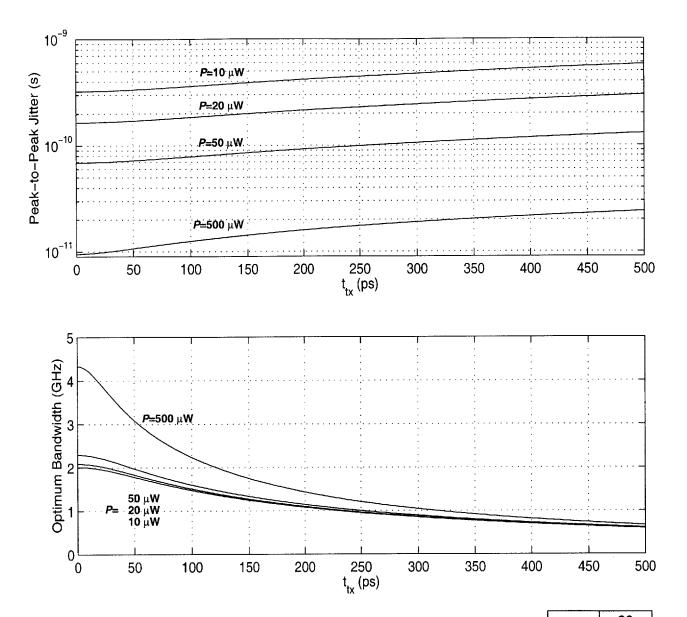

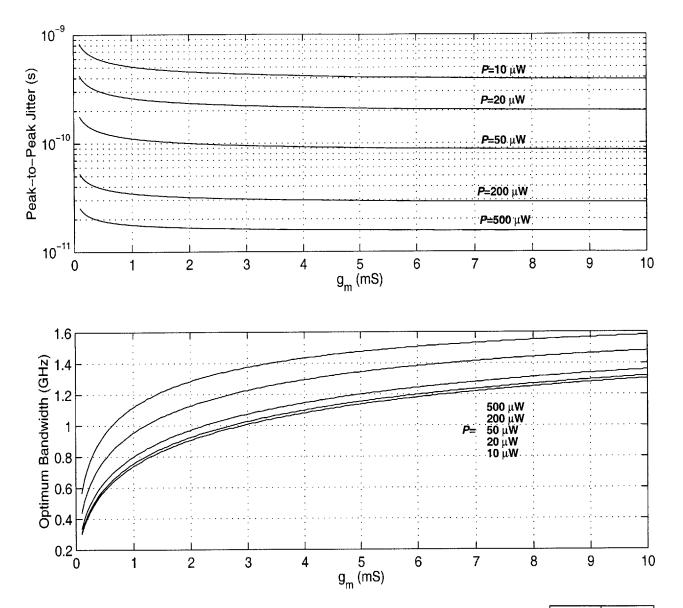

| 5.13 | Jitter vs. transmitter rise/fall time                                                   |

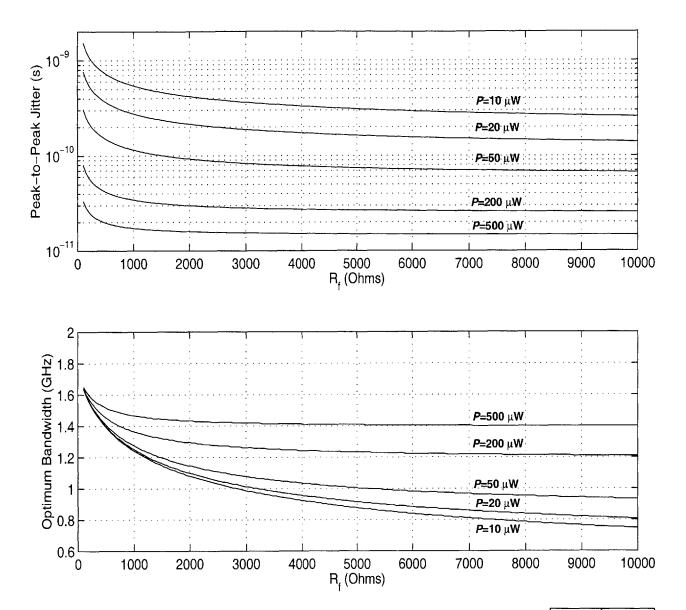

| 5.14 | Jitter vs. transimpedance amplifier feedback resistance                                 |

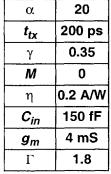

| 5.15 | Jitter vs. transimpedance amplifier FET transconductance                                |

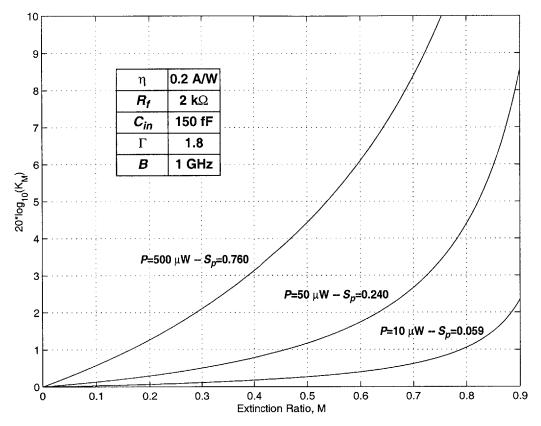

| 5.16 | Power penalty for non-zero extinction ratio                                             |

| 5.17 | Power penalty for supply noise                                                          |

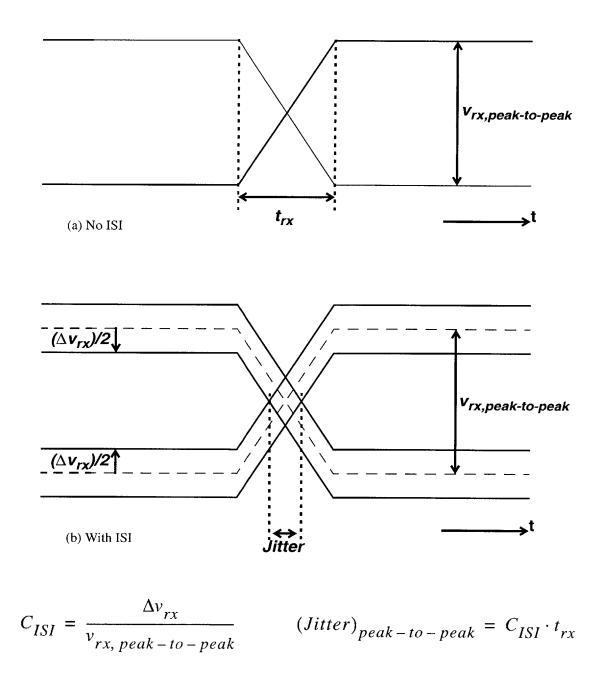

| 5.18 | Eye closure and jitter due to intersymbol interference                                  |

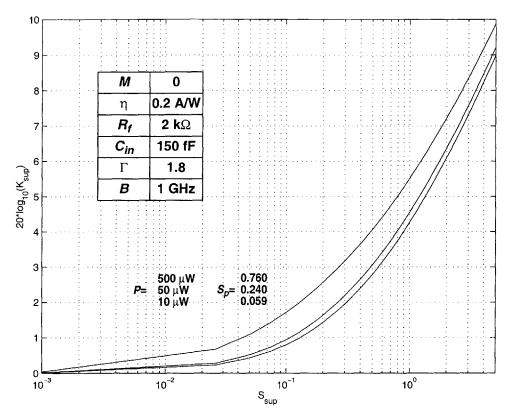

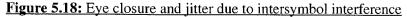

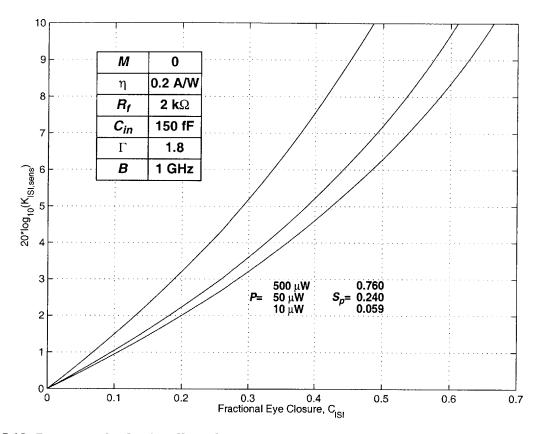

| 5.19 | Power penalty for the effect of ISI on sensitivity                                      |

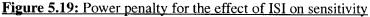

| 5.20 | Power penalty for the effect of ISI on jitter                                           |

| 6.1  | L-I characteristics of a generic laser diode                                            |

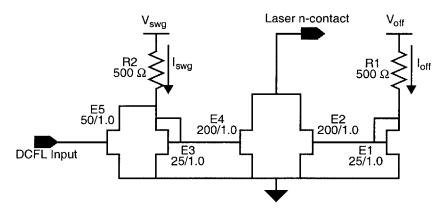

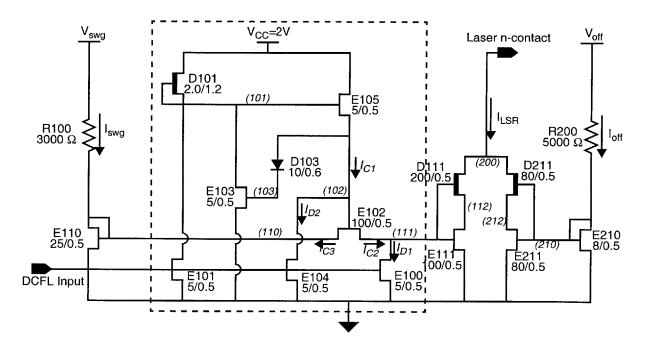

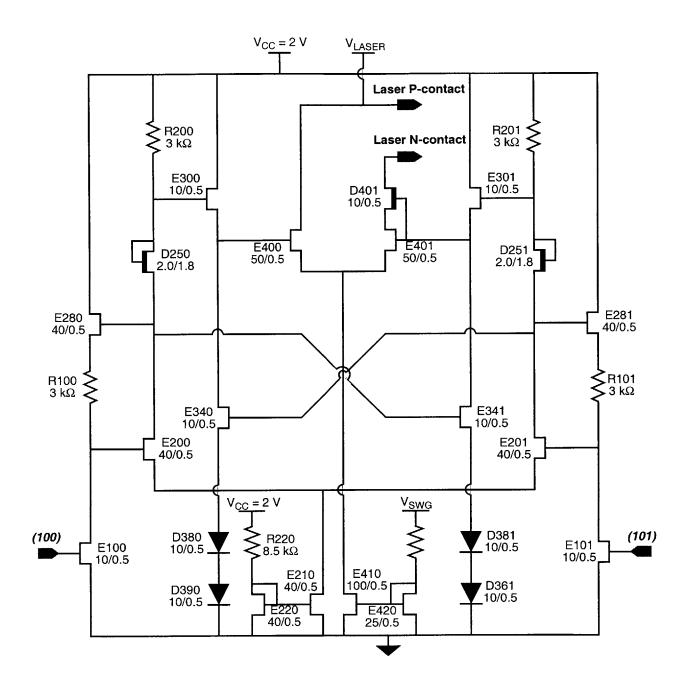

| 6.2  | Schematic of first-generation switched current mirror laser driver                      |

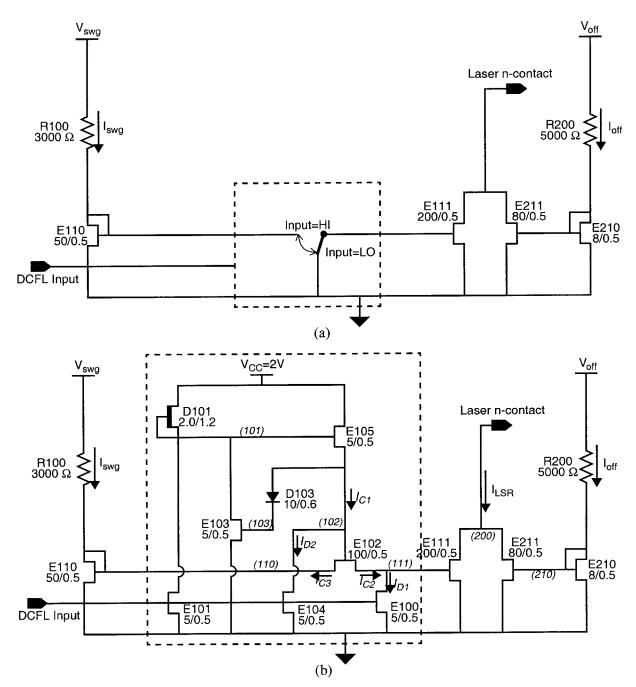

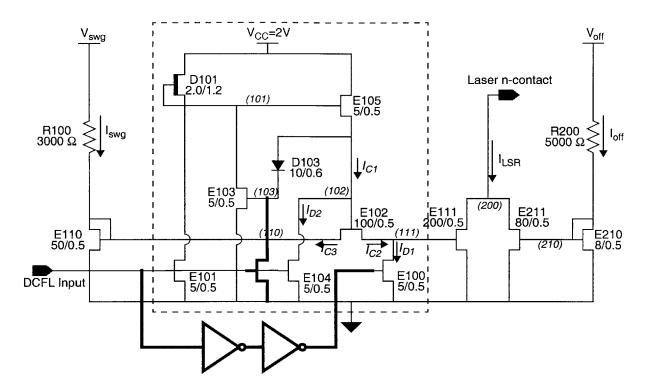

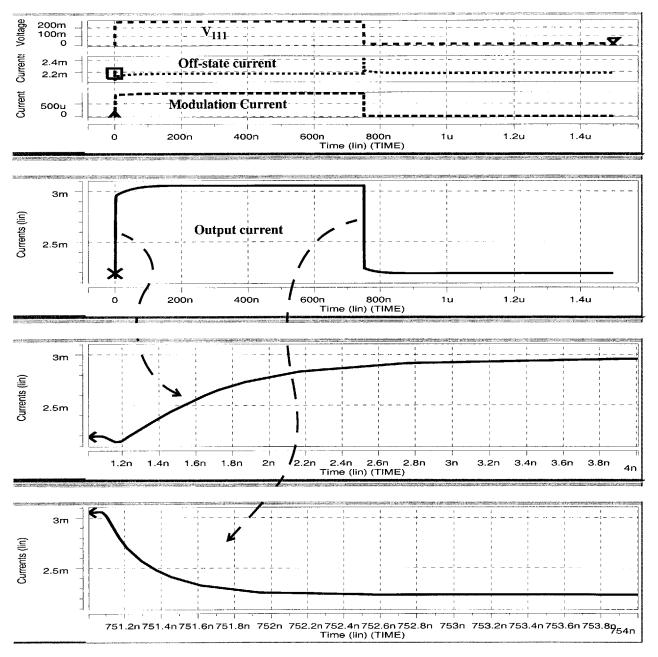

| 6.3  | Schematic of an active switched current mirror laser driver                             |

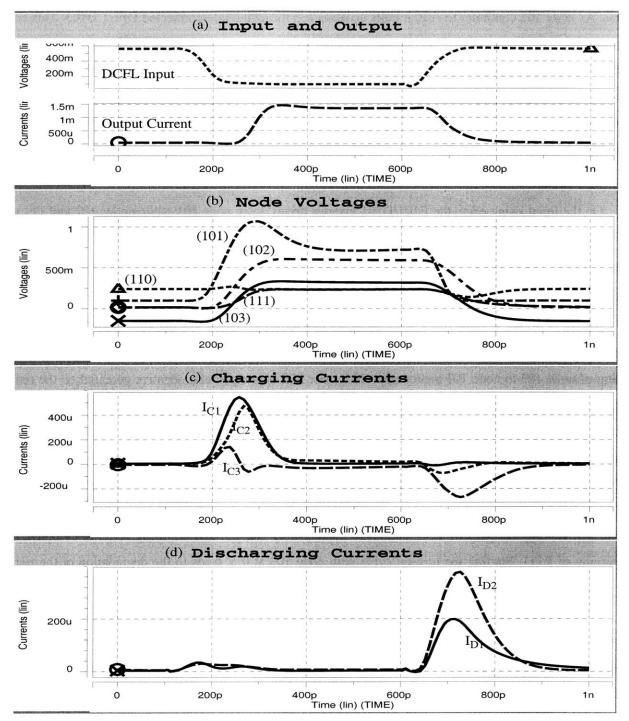

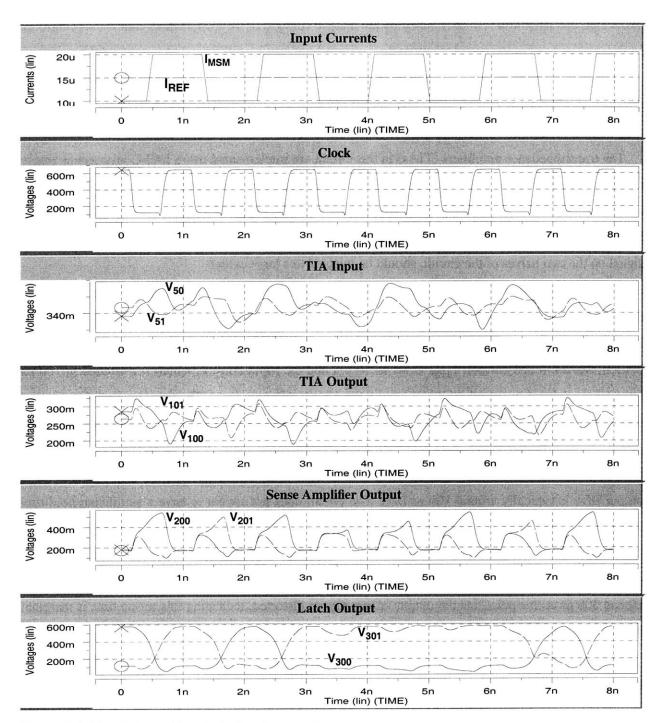

| 6.4  | Simulation of active switched current mirror laser driver                               |

| 6.5  | Modifications to laser driver of Figure 6.3                                             |

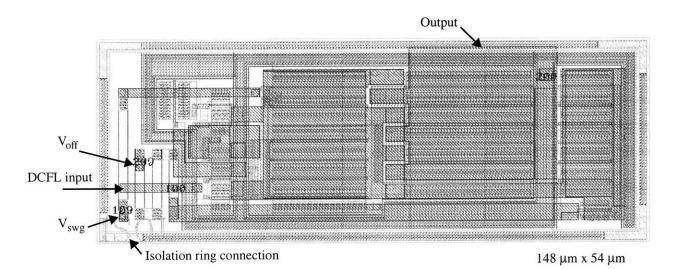

| 6.6  | Layout of the active switched current mirror laser driver                               |

| 6.7  | Layout of die cut from MIT-OEIC-7 for laser driver characterization                     |

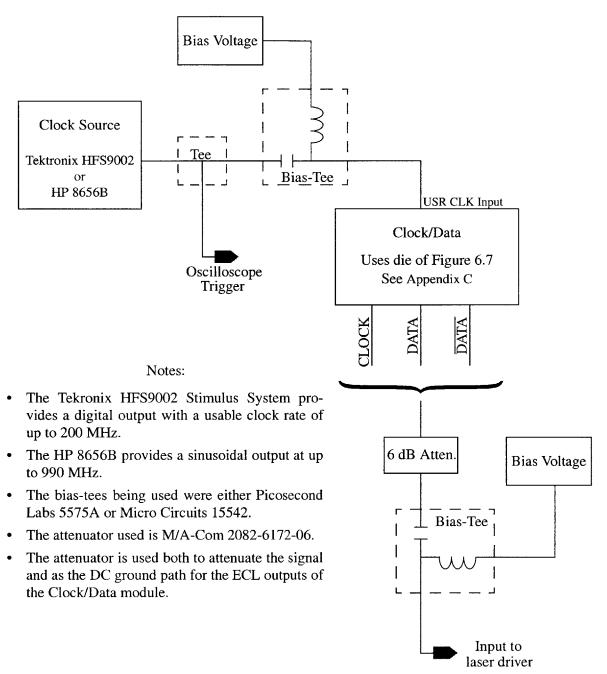

| 6.8  | Signal source for characterization of laser driver                                      |

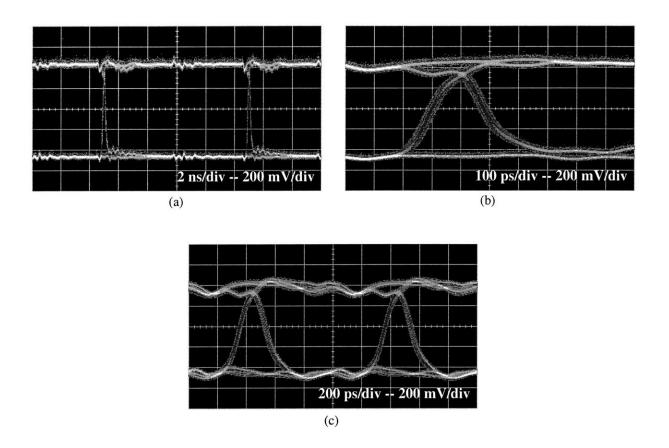

| 6.9  | Data signal used to characterize laser driver                                           |

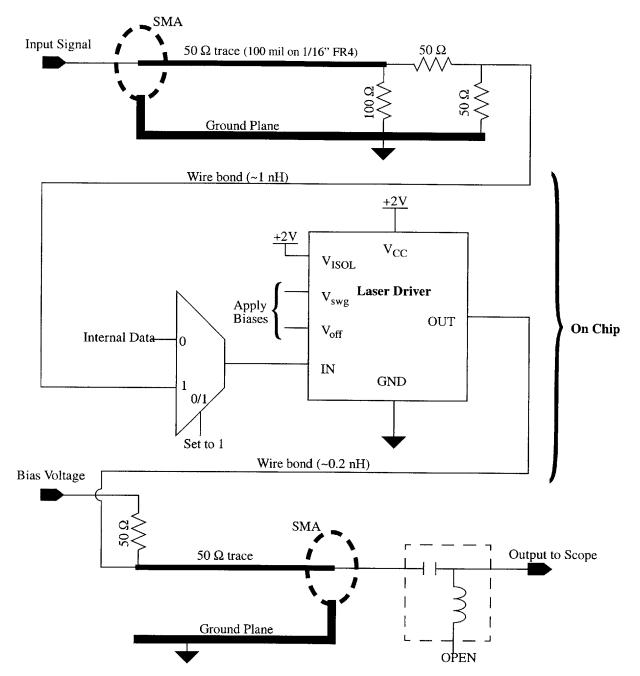

| 6.10 | Signal path for electrical characterization of the laser driver                         |

| 6.11 | Parasitic coupling of input to output in laser driver electrical test module            |

|      |                                                                                         |

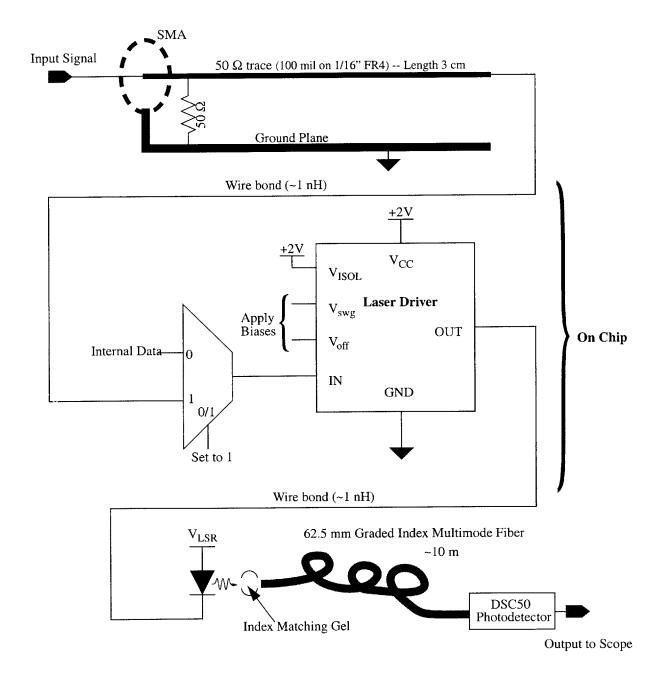

| 6.12 | Signal path for optical characterization of the laser driver                                                                                              | 250 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

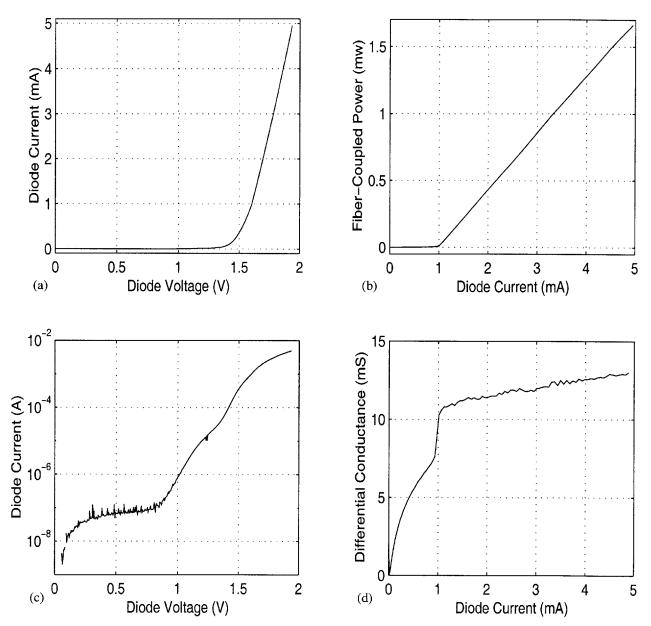

| 6.13 | Static characteristics of a typical VCSEL                                                                                                                 | 251 |

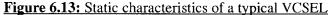

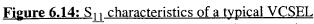

| 6.14 | S <sub>11</sub> characteristics of a typical VCSEL                                                                                                        | 253 |

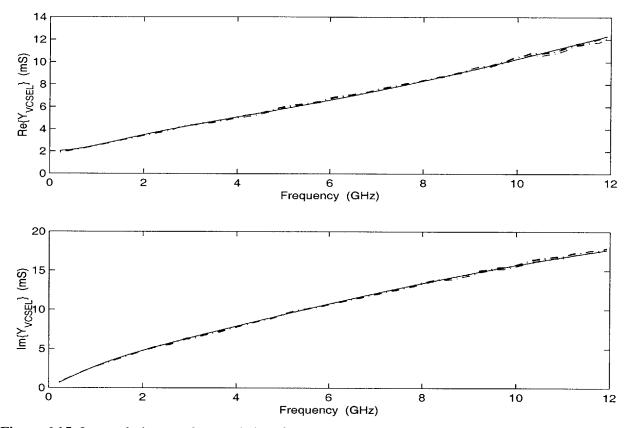

| 6.15 | Input admittance characteristics of a typical VCSEL                                                                                                       | 254 |

| 6.16 | Equivalent small signal input circuit for a typical VCSEL.                                                                                                | 254 |

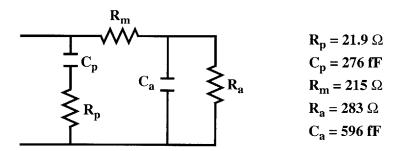

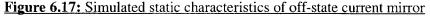

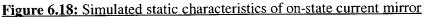

| 6.17 | Simulated static characteristics of off-state current mirror.                                                                                             | 256 |

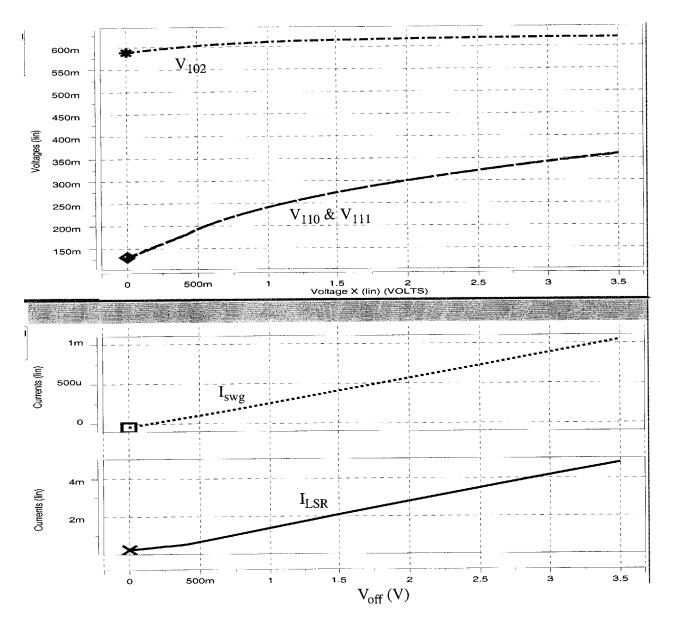

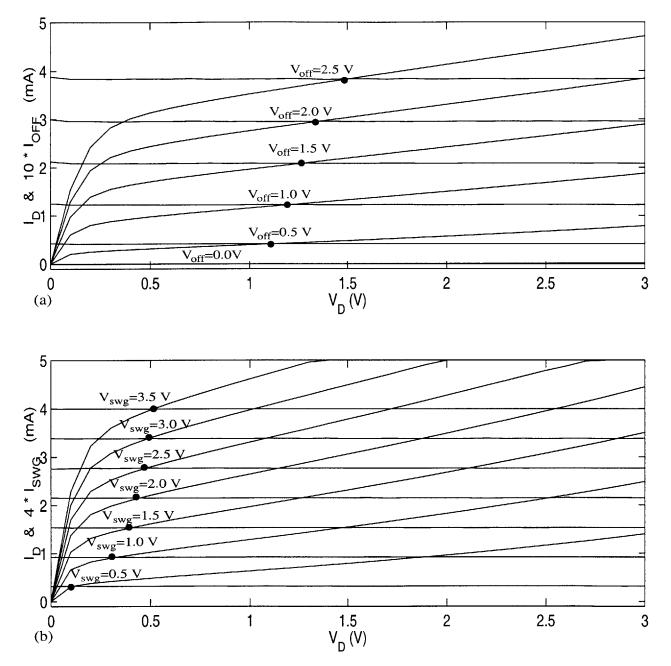

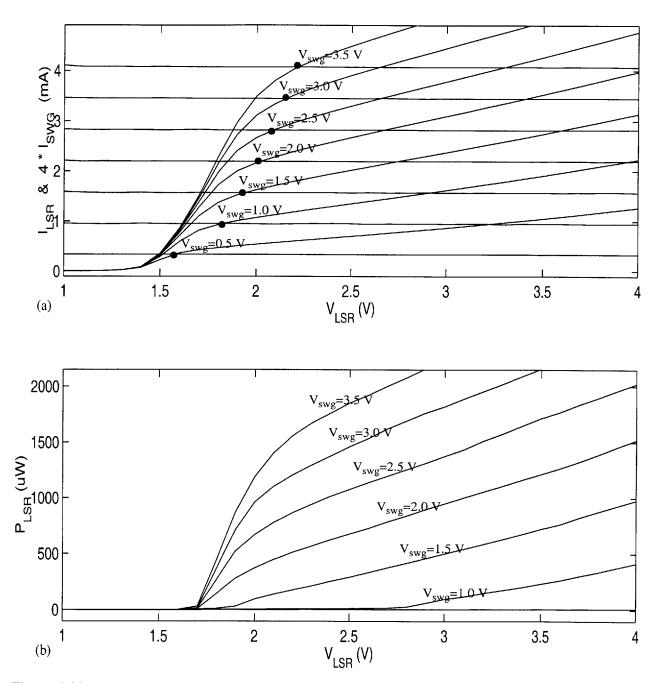

| 6.18 | Simulated static characteristics of on-state current mirror                                                                                               | 257 |

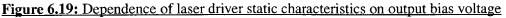

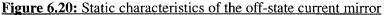

| 6.19 | Dependence of laser driver static characteristics on output bias voltage                                                                                  | 259 |

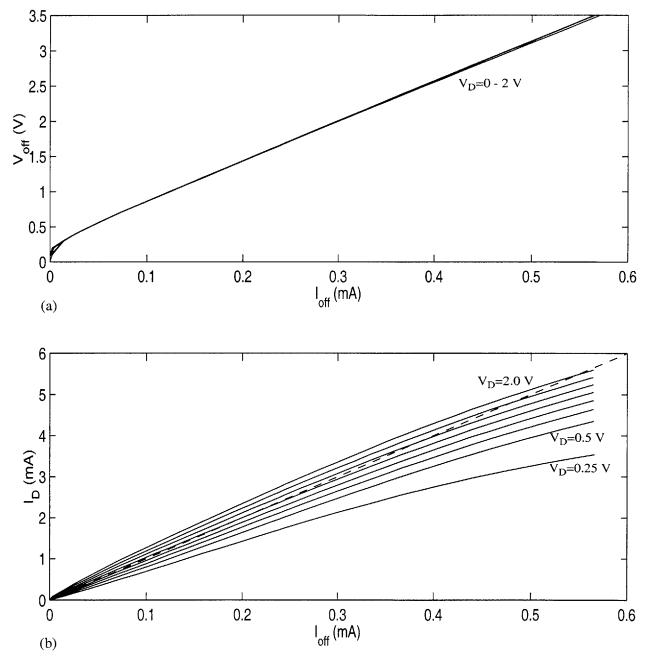

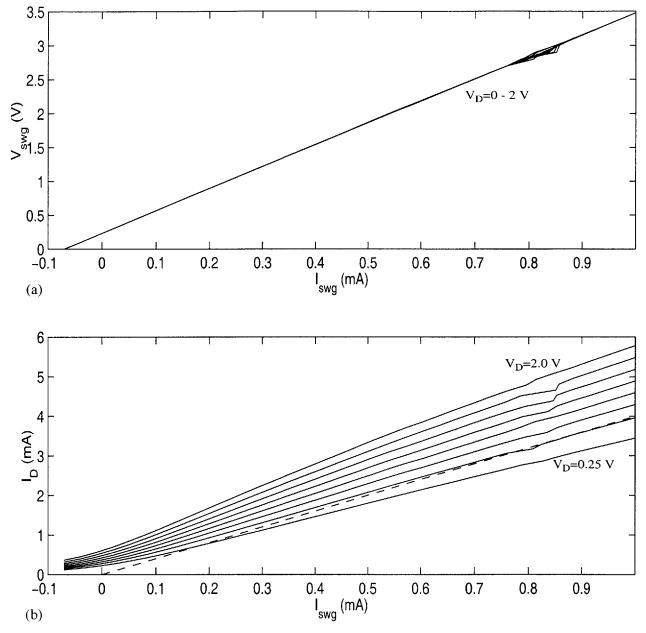

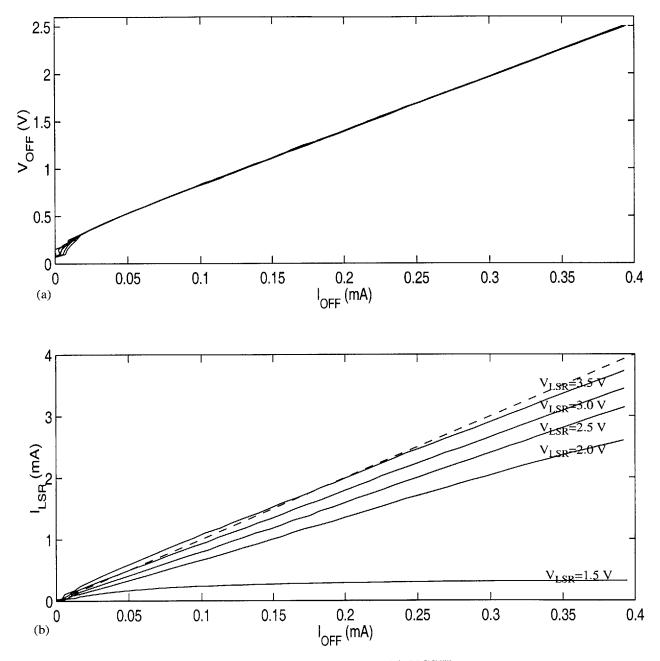

| 6.20 | Static characteristics of the off-state current mirror                                                                                                    | 260 |

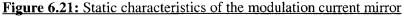

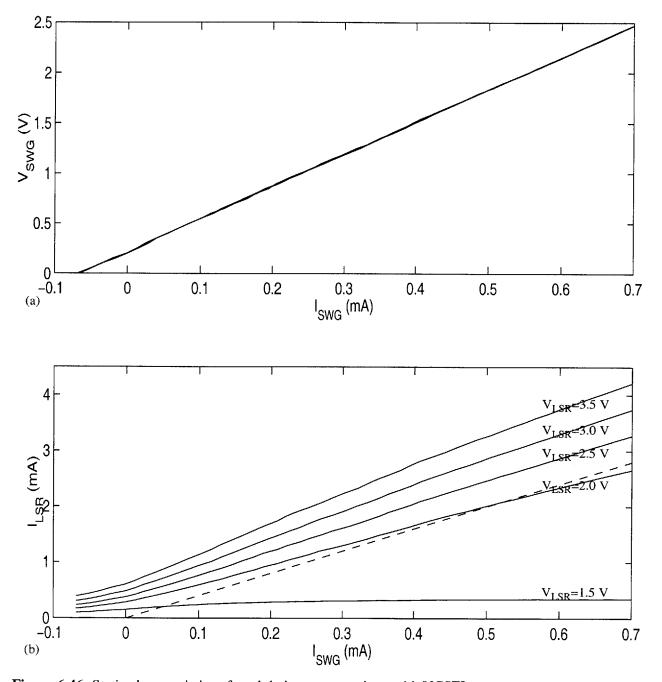

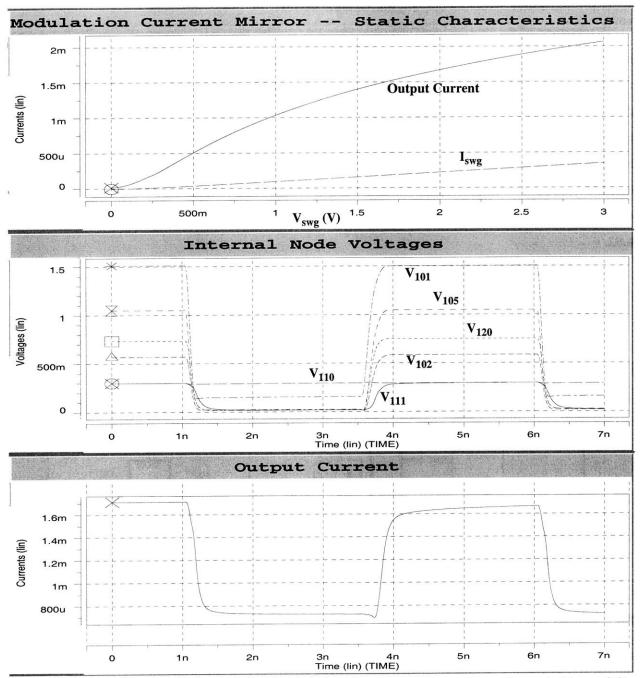

| 6.21 | Static characteristics of the modulation current mirror.                                                                                                  | 262 |

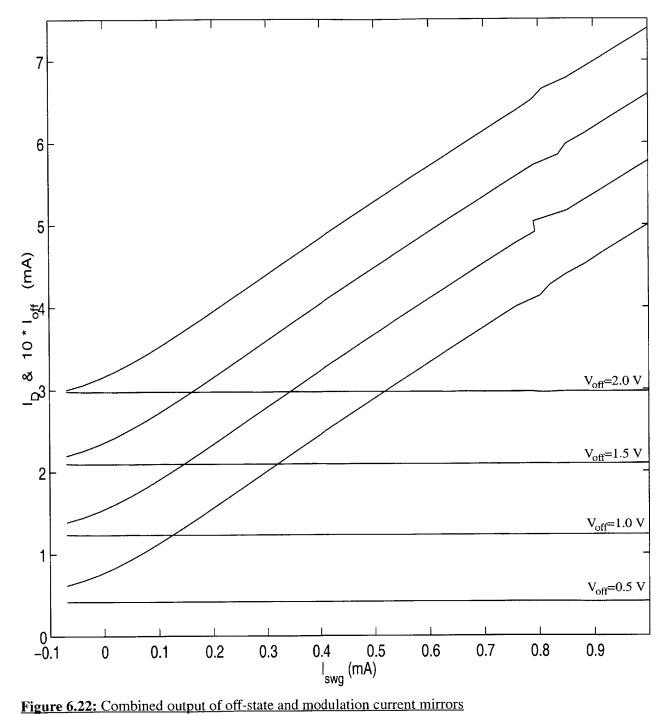

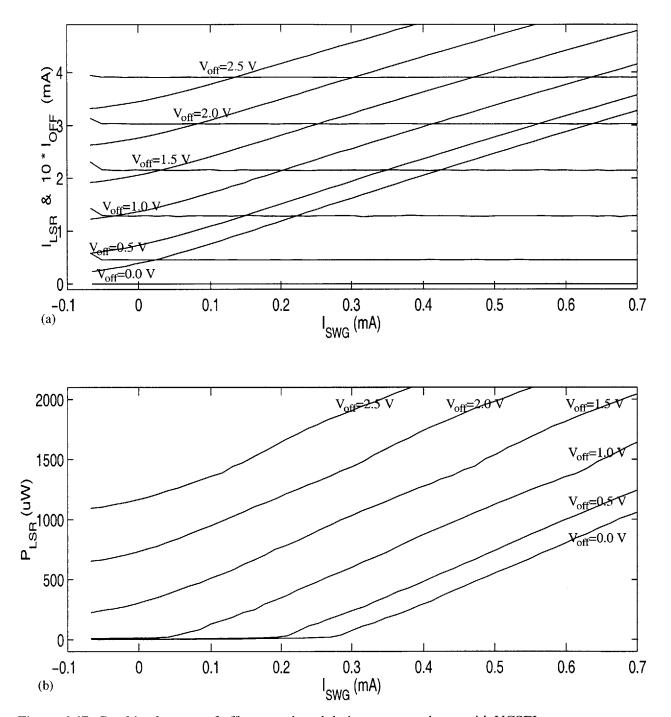

| 6.22 | Combined output of off-state and modulation current mirrors                                                                                               | 263 |

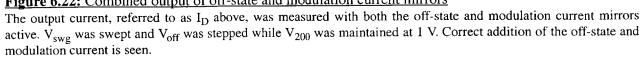

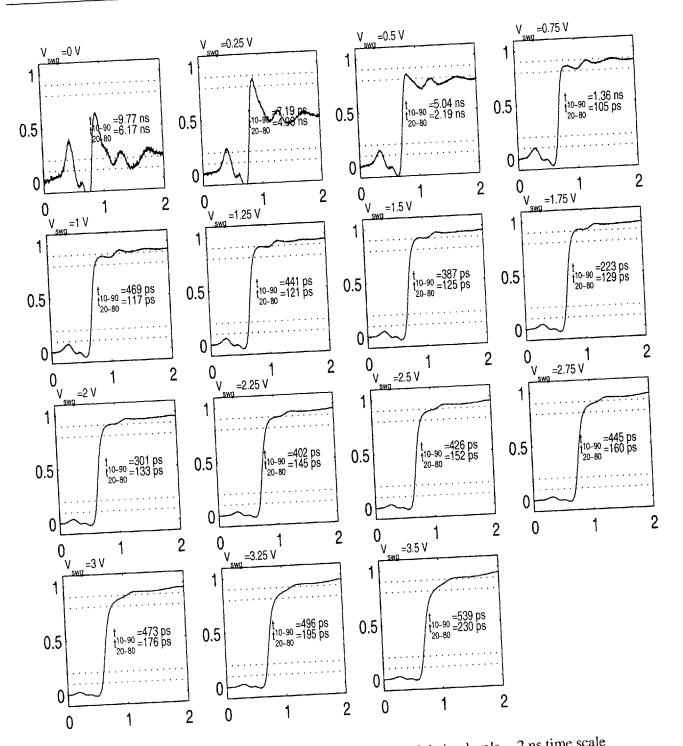

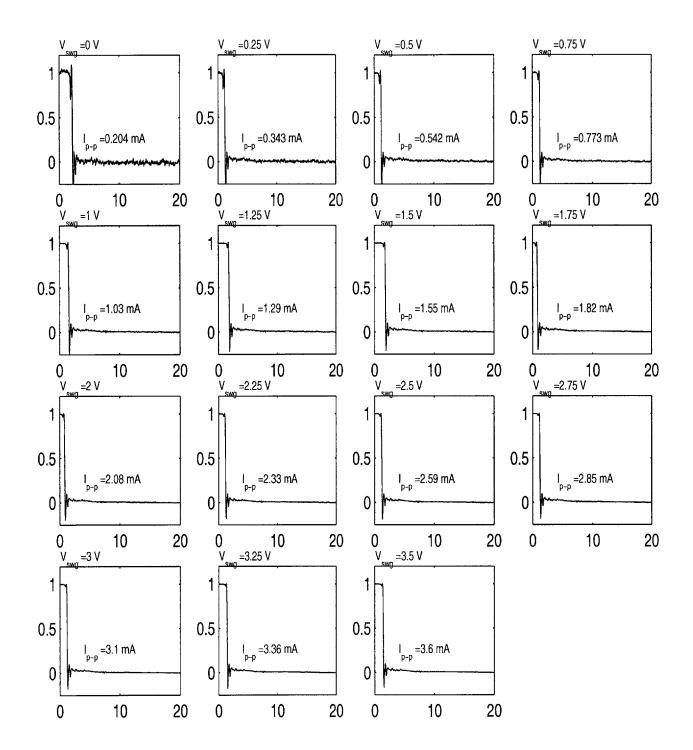

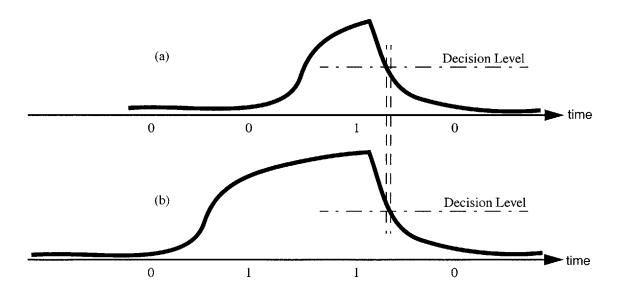

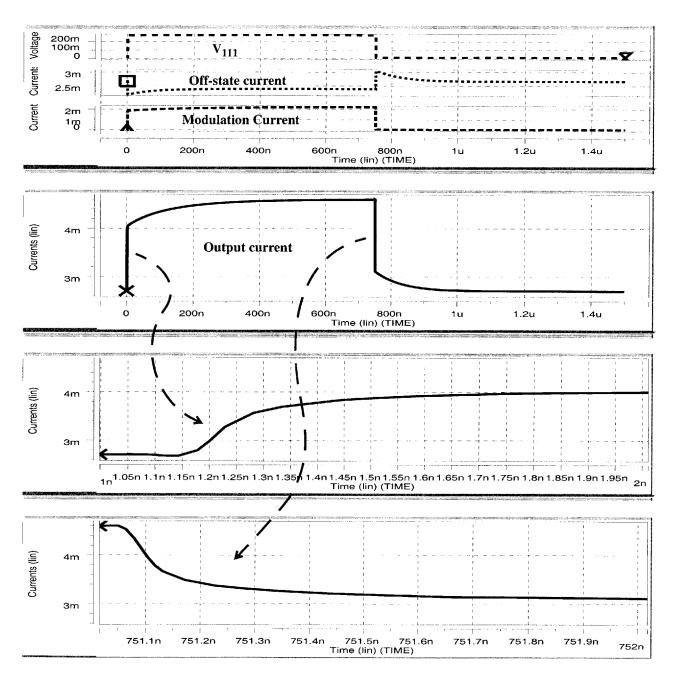

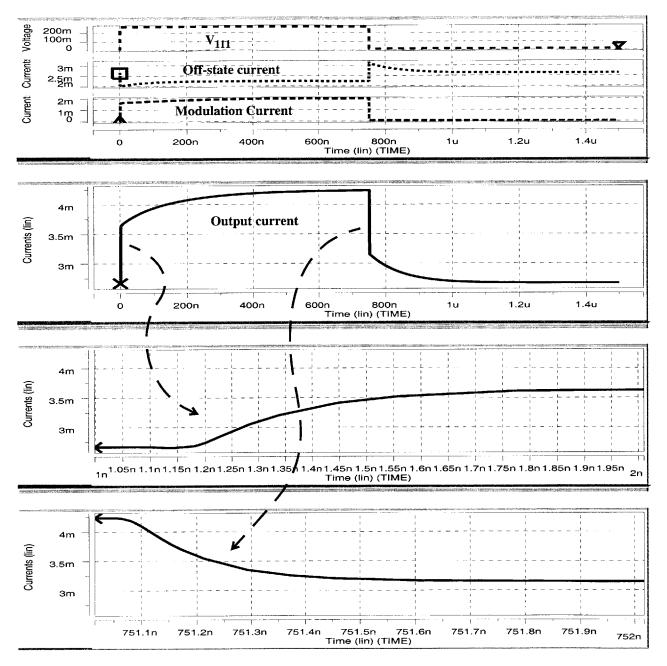

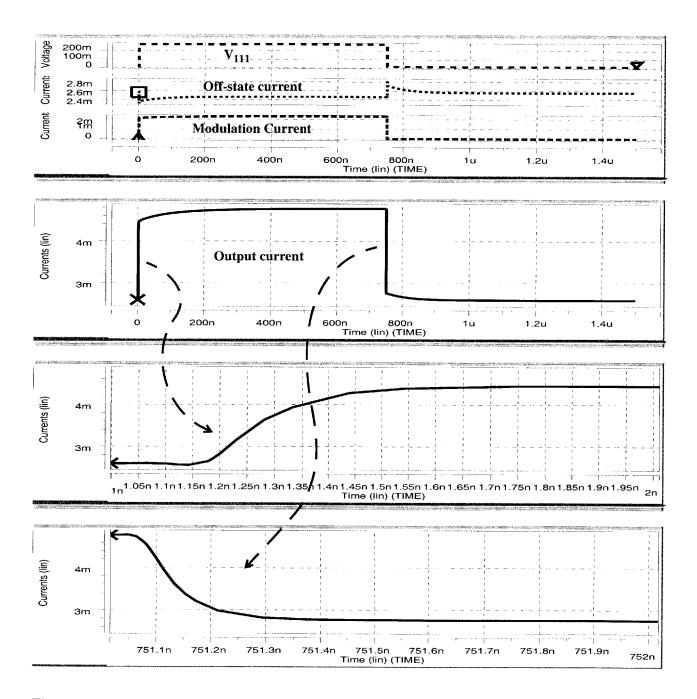

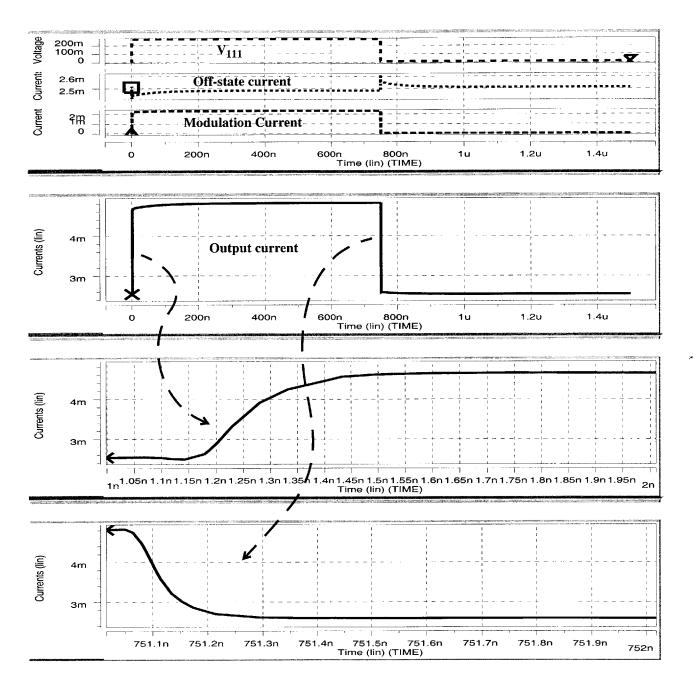

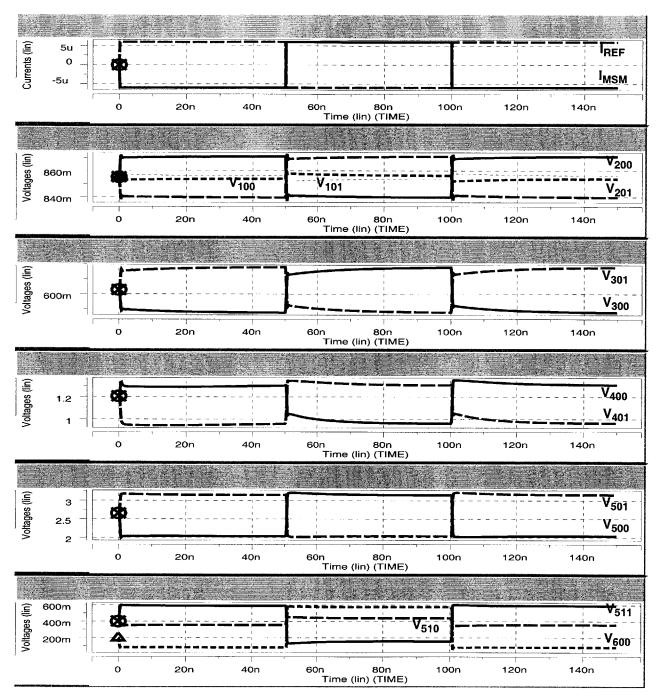

| 6.23 | Laser driver turn-on characteristics at various modulation levels 20 ns time scale                                                                        | 265 |

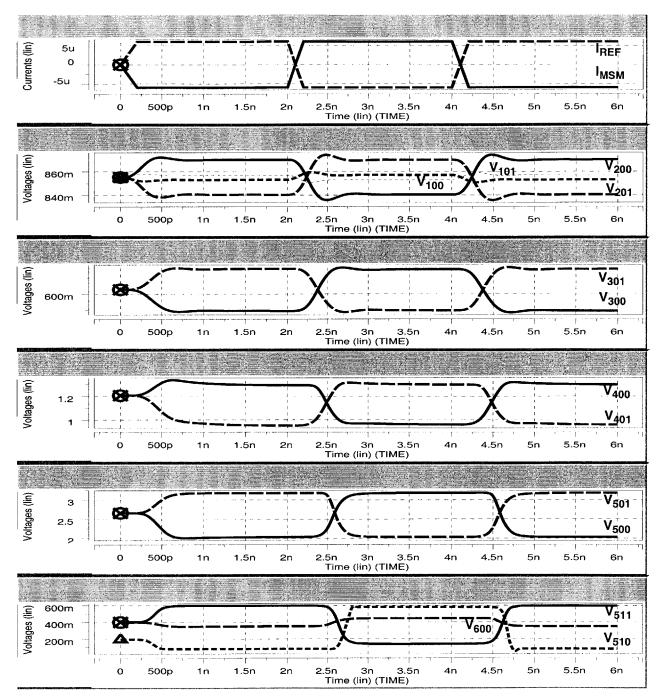

| 6.24 | Laser driver turn-on characteristics at various modulation levels 2 ns time scale                                                                         | 266 |

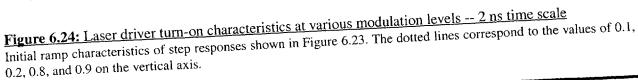

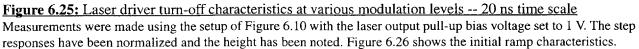

| 6.25 | Laser driver turn-off characteristics at various modulation levels 20 ns time scale                                                                       | 267 |

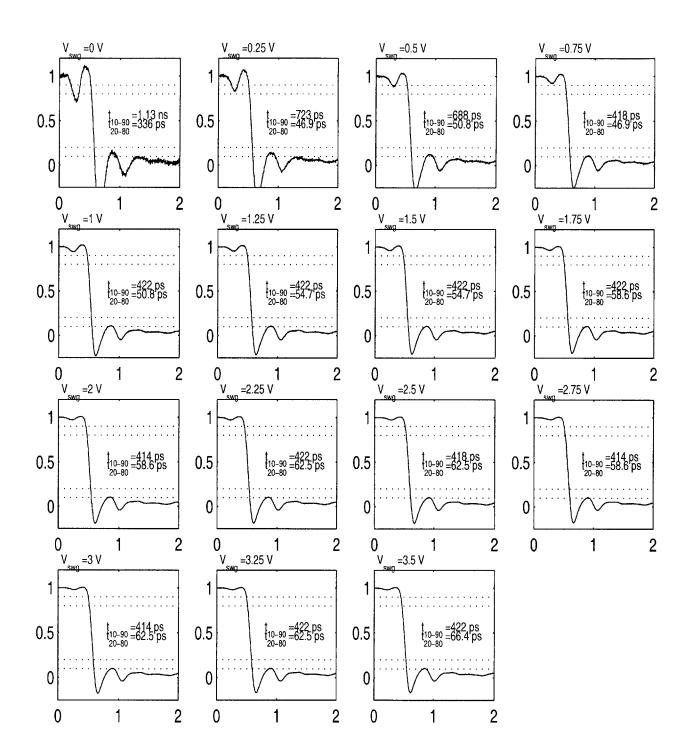

| 6.26 | Laser driver turn-off characteristics at various modulation levels 2 ns time scale                                                                        | 268 |

| 6.27 | Simulation of laser driver slow turn-on effect at low modulation level                                                                                    | 269 |

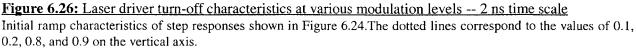

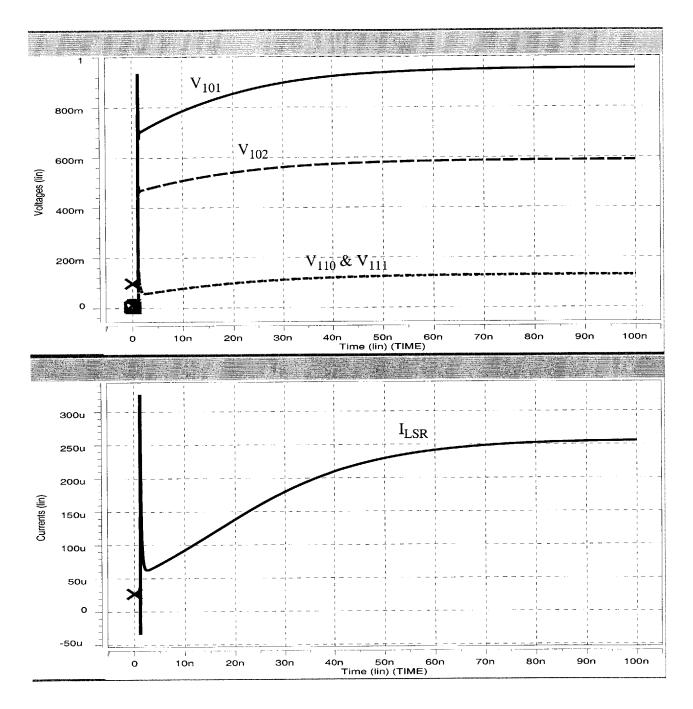

| 6.28 | Plots of rise and fall time vs. modulation bias level                                                                                                     | 273 |

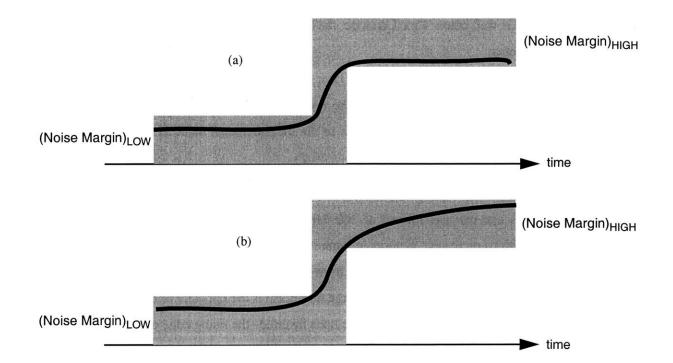

| 6.29 | Jitter caused by combined effect of slow laser driver settling and linear channel response                                                                | 276 |

| 6.30 | Comparison of transition times specifications in meeting noise margin requirements.                                                                       |     |

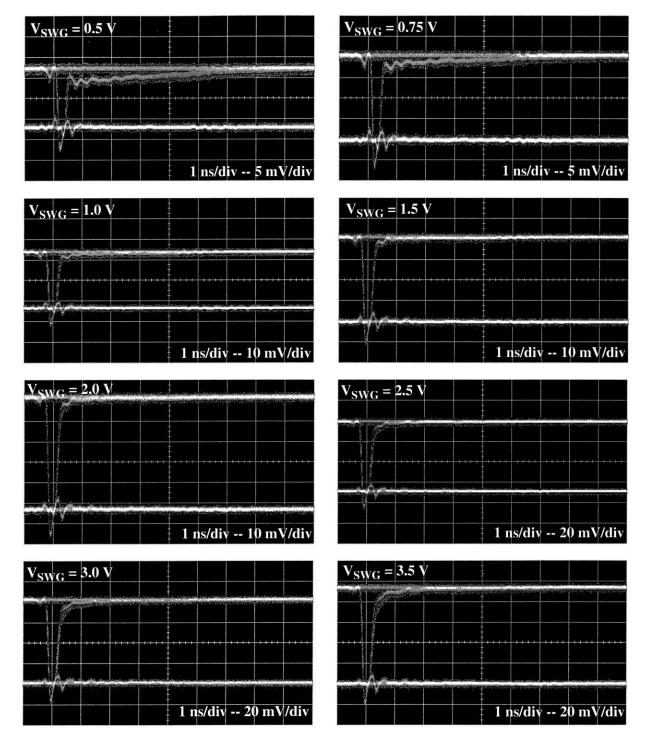

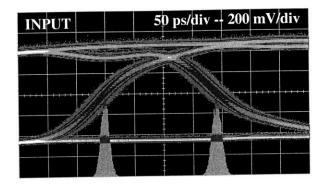

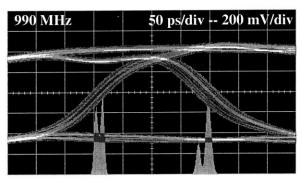

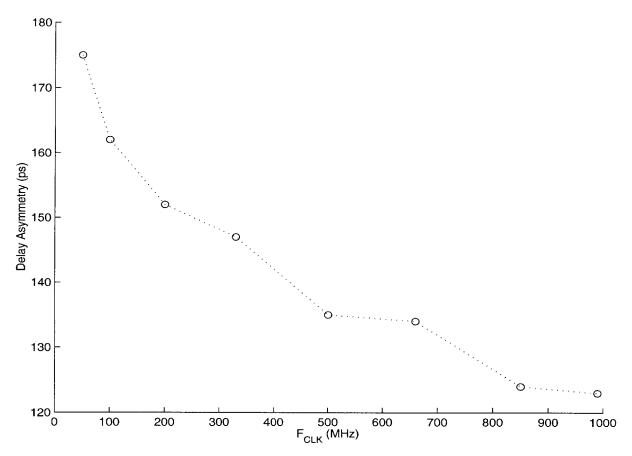

| 6.31 | 100 MHz eye pattern of laser driver output at various modulation levels                                                                                   | 279 |

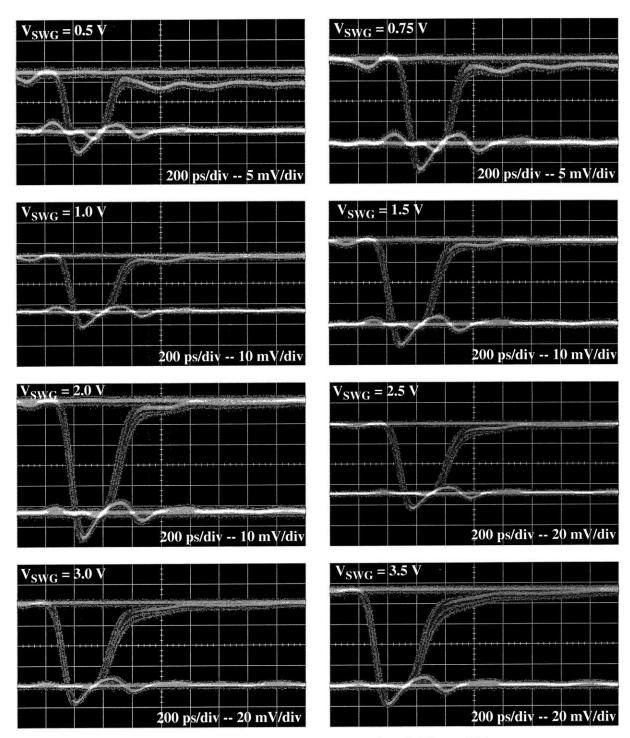

| 6.32 | Close-up of transitions in 100 MHz eye patterns given in Figure 6.31                                                                                      | 280 |

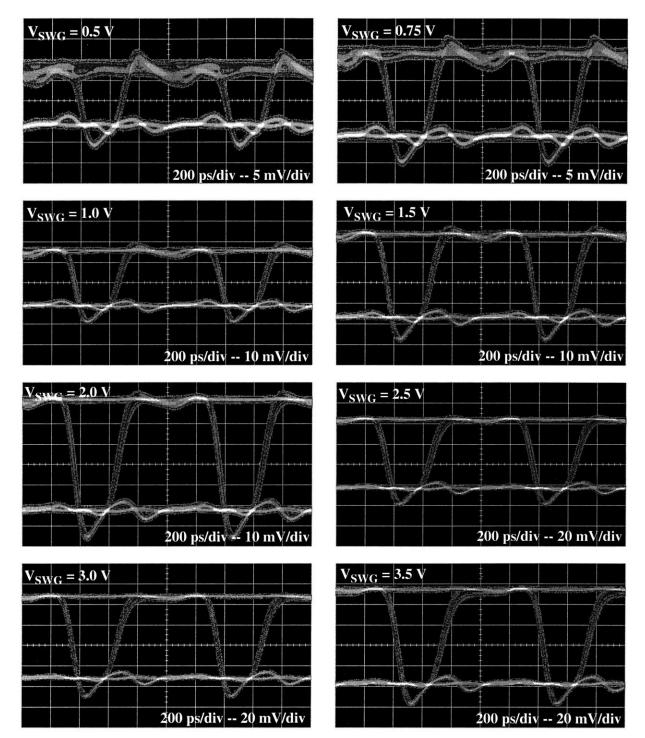

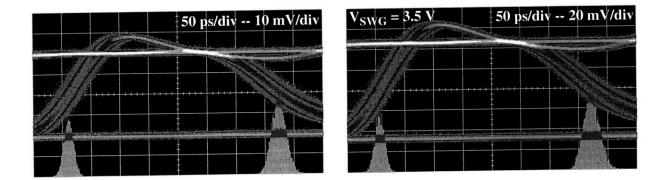

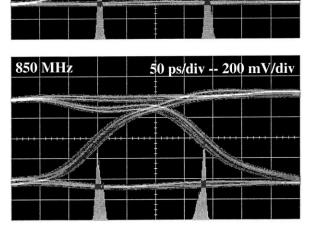

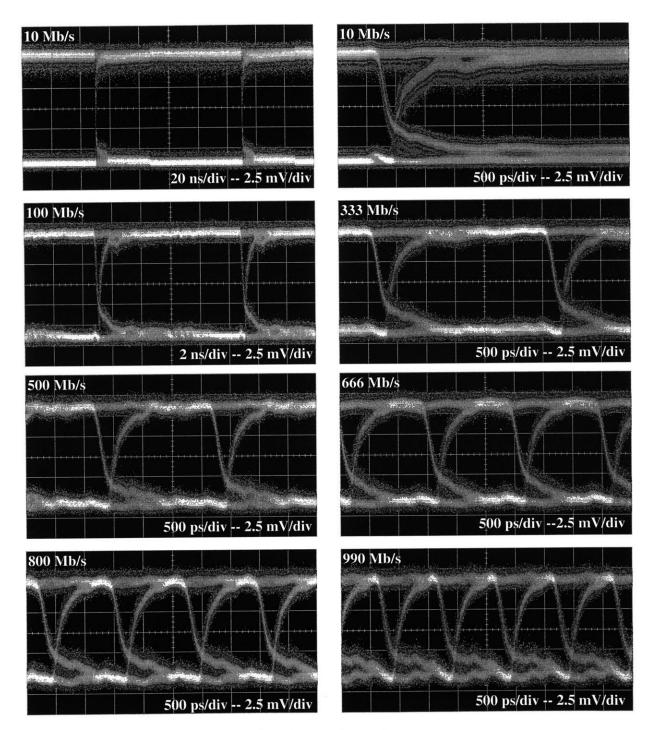

| 6.33 | 990 MHz eye pattern of laser driver output at various modulation levels                                                                                   | 281 |

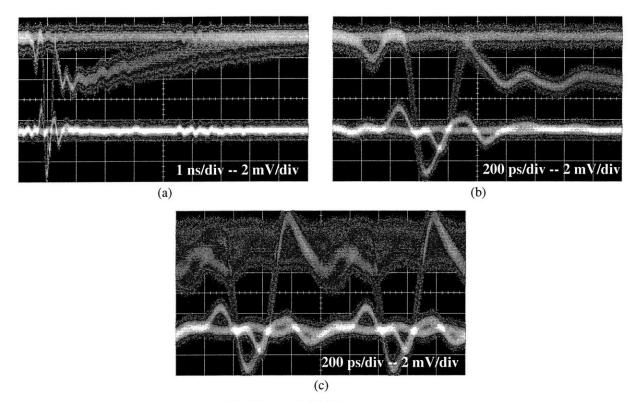

| 6.34 | Laser output eye patters for $Vswg = 0.25 V \dots $ |     |

| 6.35 | Edge timing vs. modulation level at 100 Mb/s                                                                                                              | 285 |

| 6.36 | Edge timing vs. modulation level at 990 Mb/s                                                                                                              | 286 |

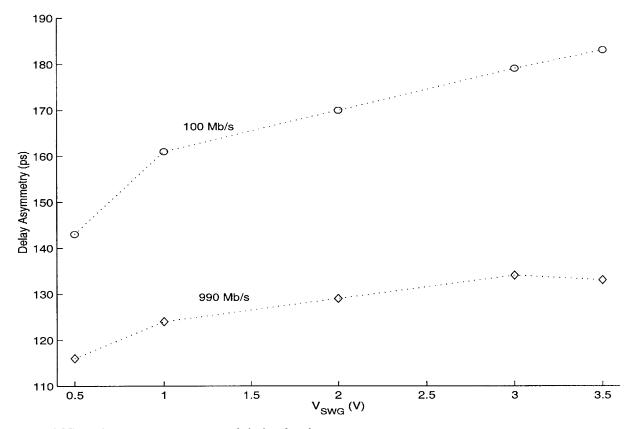

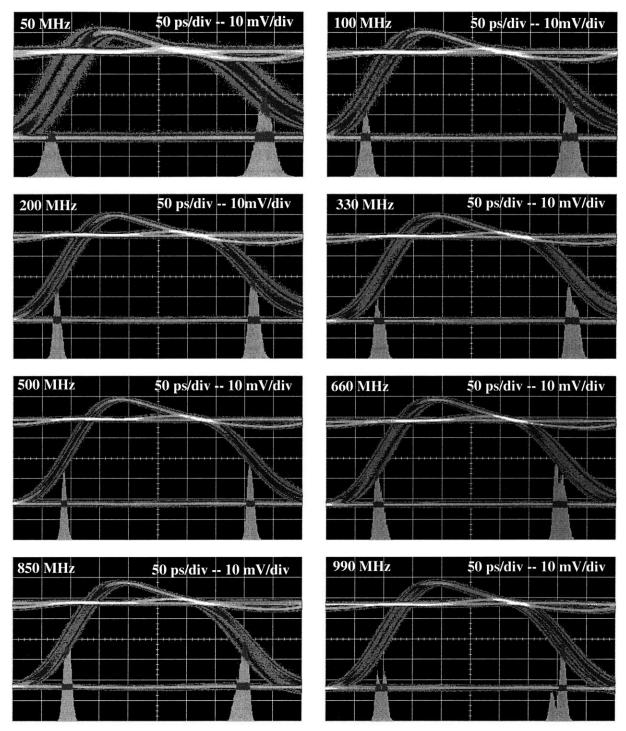

| 6.37 | Delay asymmetry vs. modulation level.                                                                                                                     | 289 |

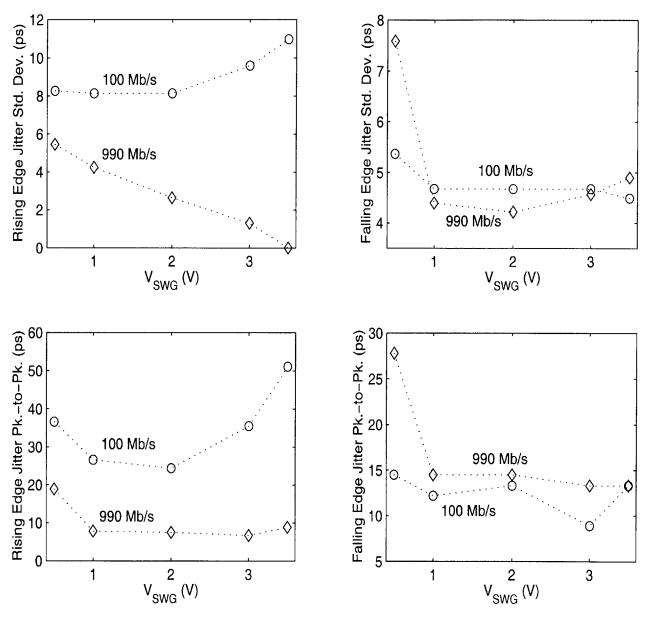

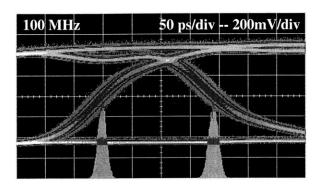

| 6.38 | Jitter vs. modulation level                                                                                                                               | 290 |

| 6.39 | Input signal edge timing vs. bit-rate                                                                                                                     | 292 |

| 6.40 | Edge timing vs. bit-rate with Vswg=1.5 V                                                                                                                  |     |

| 6.41 | Delay asymmetry vs. bit rate for Vswg=1.5 V                                                                                                               |     |

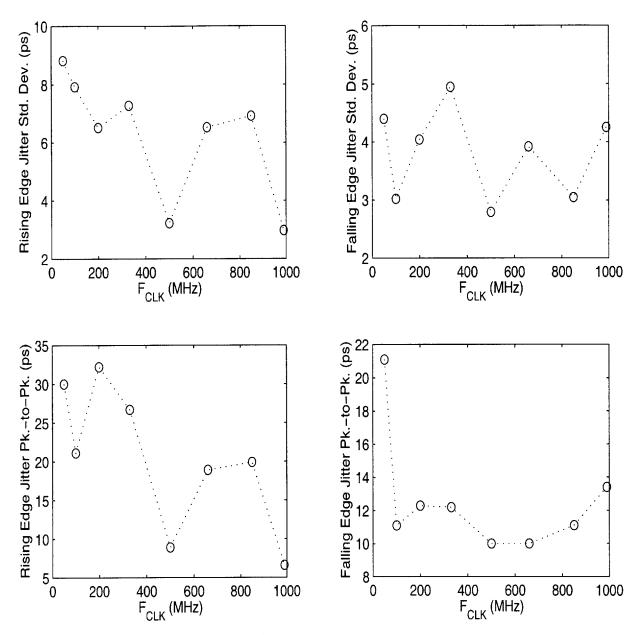

| 6.42 | Jitter vs. bit-rate for Vswg=1.5 V.                                                                                                                       |     |

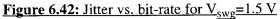

| 6.43 | Dependence of off-state current mirror on VCSEL supply voltage                                                                                            | 299 |

| 6.44 | Dependence of modulation current mirror on VCSEL supply voltage.                                                                                          |     |

| 6.45 | Static characteristics of off-state current mirror with VCSEL                                                                                             |     |

| 6.46 | Static characteristics of modulation current mirror with VCSEL                                                                                            |     |

| 6.47 | Combined output of off-state and modulation current mirrors with VCSEL                                                                                    |     |

|      |                                                                                                                                                           |     |

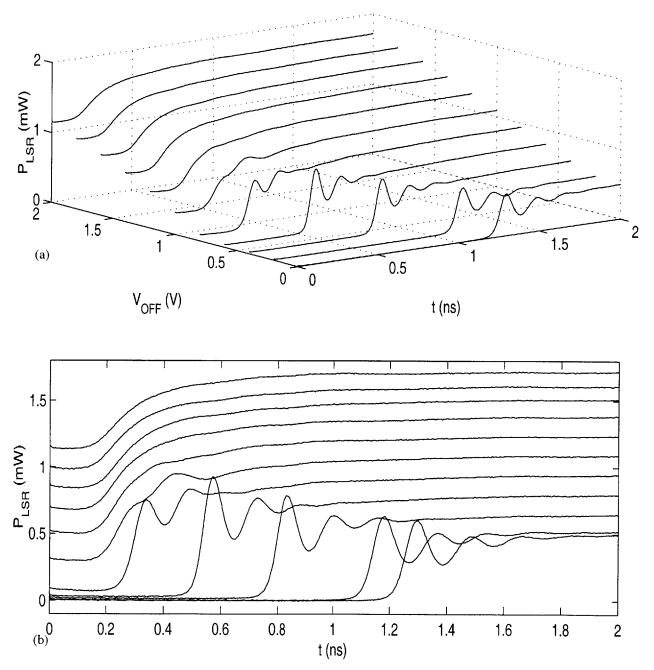

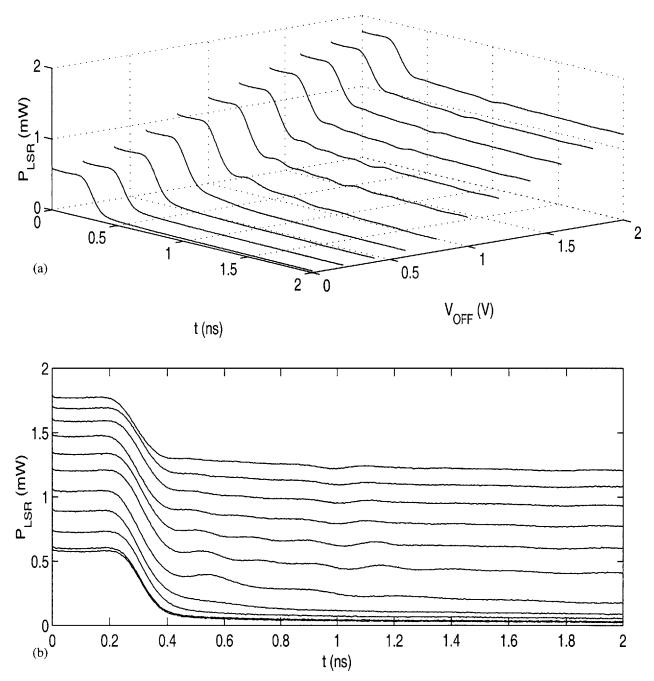

| 6.48 | Laser rising-edge dependence on off-state level                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------|

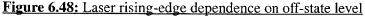

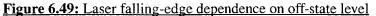

| 6.49 | Laser falling-edge dependence on off-state level                                                                                   |

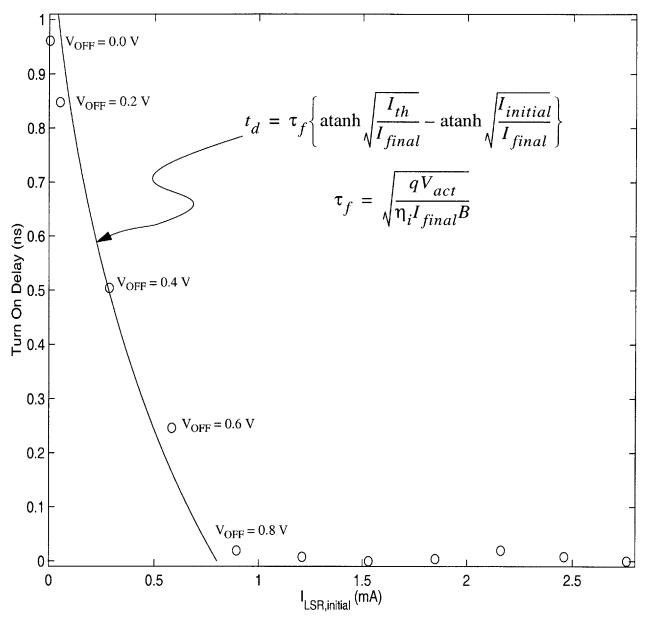

| 6.50 | Turn-on delay dependence on off-state level                                                                                        |

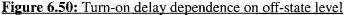

| 6.51 | Laser rising-edge dependence on modulation level                                                                                   |

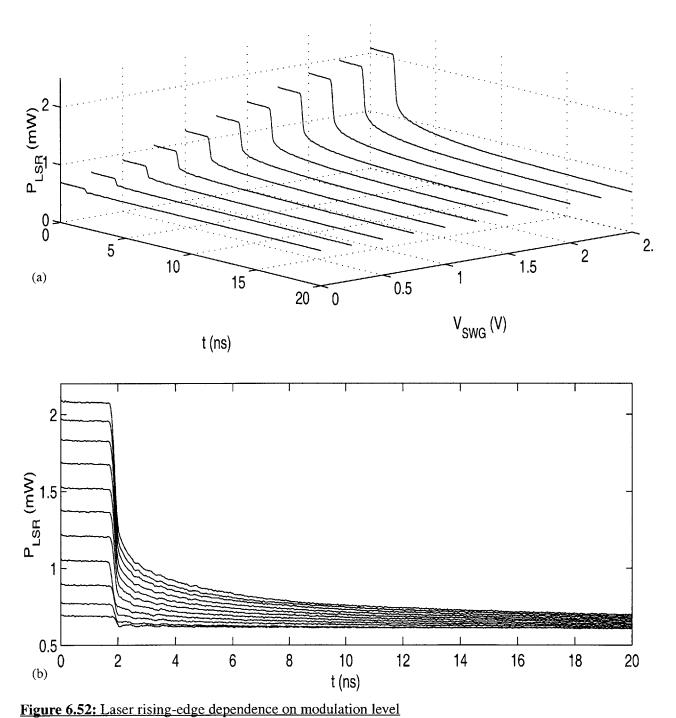

| 6.52 | Laser rising-edge dependence on modulation level                                                                                   |

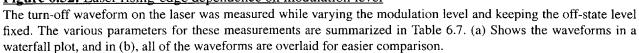

| 6.53 | Normalized optical transition waveforms at various modulation levels                                                               |

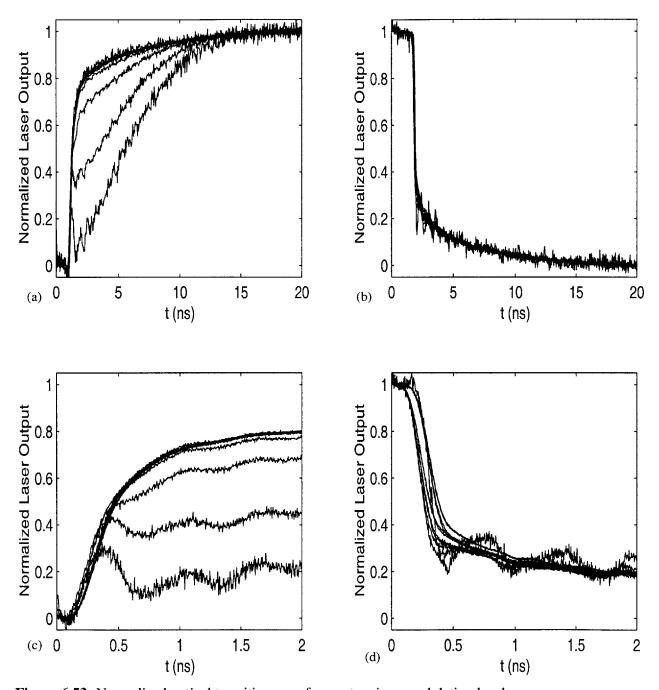

| 6.54 | Transition times of optical switching waveforms measure at various modulation levels 314                                           |

| 6.55 | Simulation of laser driver loaded by VCSEL equivalent input circuit shown in Figure 6.16 316                                       |

| 6.56 | Simulation of laser driver loaded by a 500 $\Omega$ resistor                                                                       |

| 6.57 | Simulation of laser driver loaded by an 85 $\Omega$ resistor                                                                       |

| 6.58 | Simulation of laser driver loaded by an 25 $\Omega$ resistor                                                                       |

| 6.59 | Modification of the laser driver to allow large resistive loads                                                                    |

| 6.60 | Modified laser driver simulated with 500 $\Omega$ load $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 321$ |

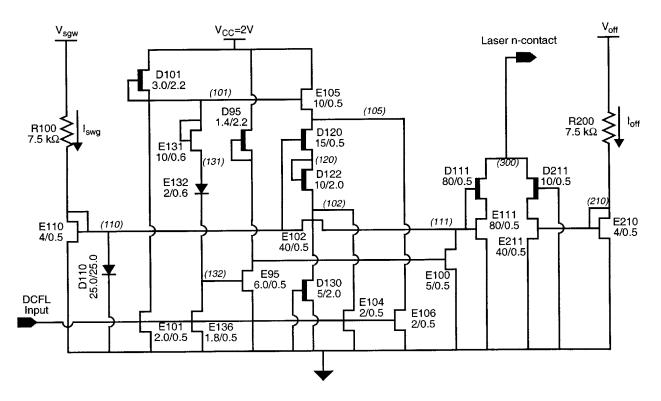

| 6.61 | An improved active switched current mirror laser driver                                                                            |

| 6.62 | Simulation of the improved active switched current mirror laser driver shown in Figure 6.61 . 324                                  |

| 6.63 | Schematic of a low-power differential laser driver                                                                                 |

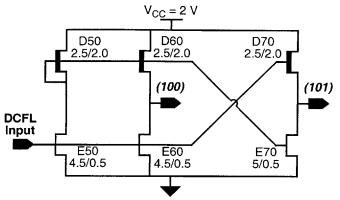

| 6.64 | Circuit for generation of complementary logic signals                                                                              |

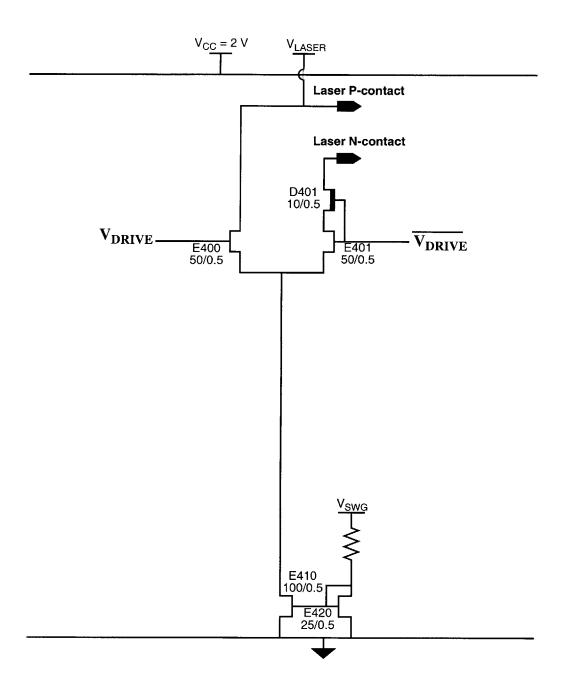

| 6.65 | Third stage of the differential laser driver                                                                                       |

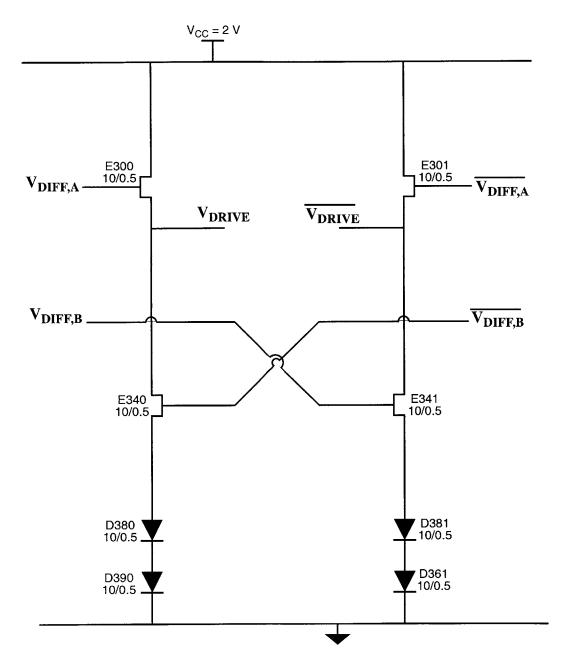

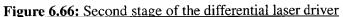

| 6.66 | Second stage of the differential laser driver                                                                                      |

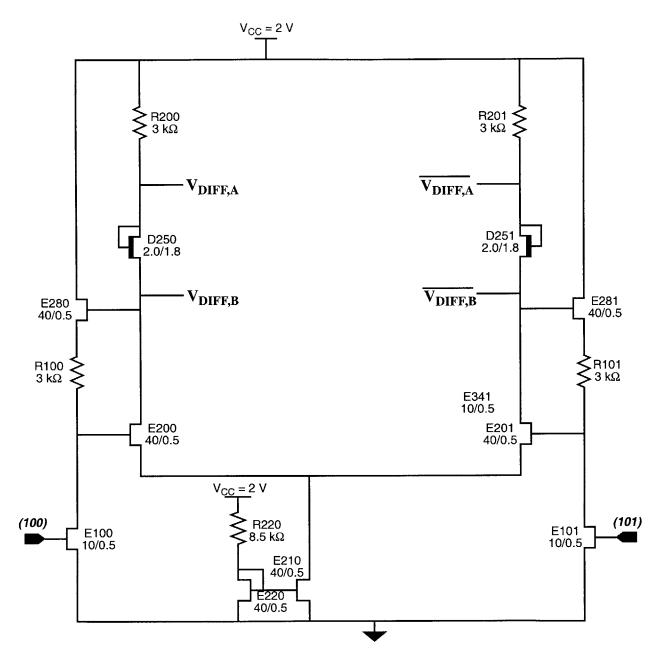

| 6.67 | First stage of the differential laser driver                                                                                       |

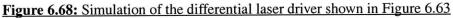

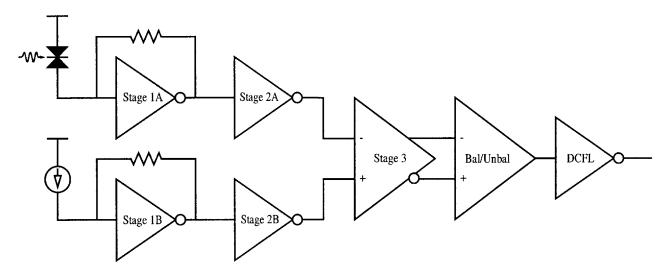

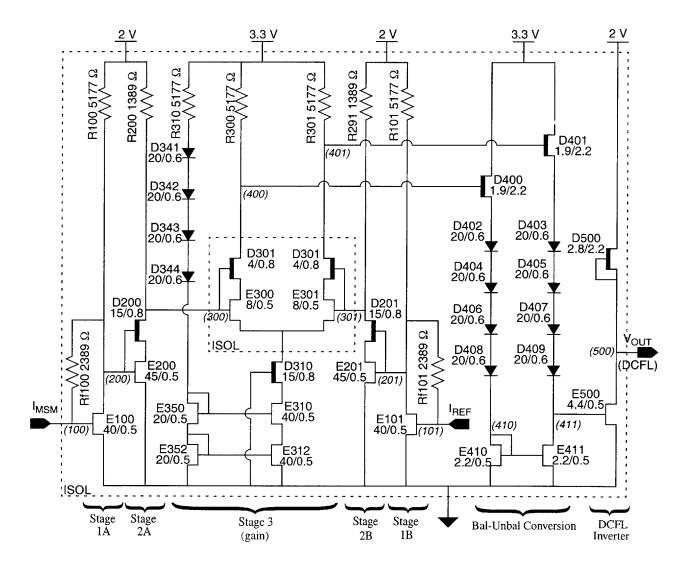

| 6.68 | Simulation of the differential laser driver shown in Figure 6.63                                                                   |

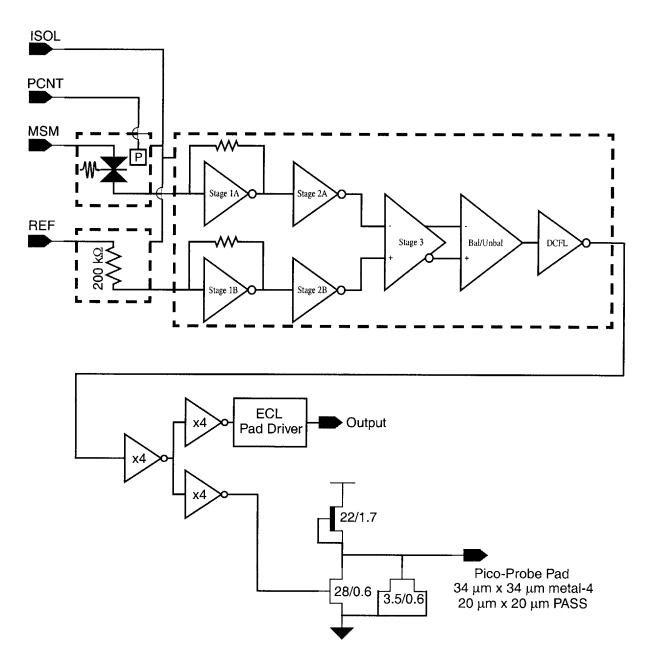

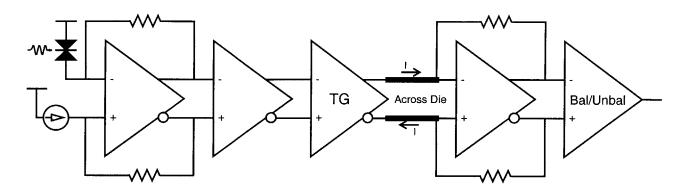

| 7.1  | Block representation of a low-power continuous time receiver                                                                       |

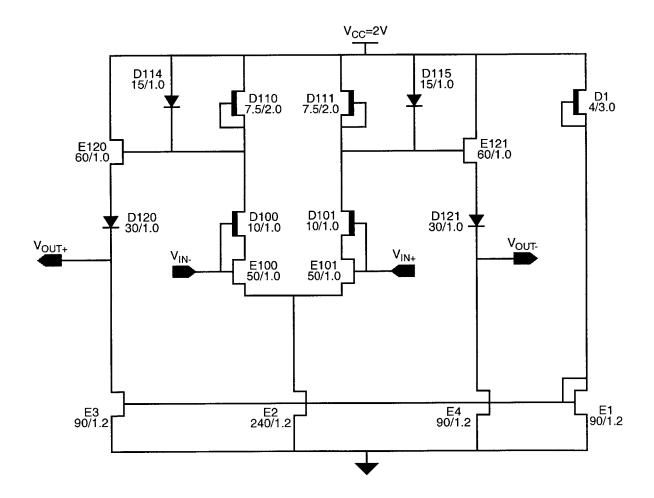

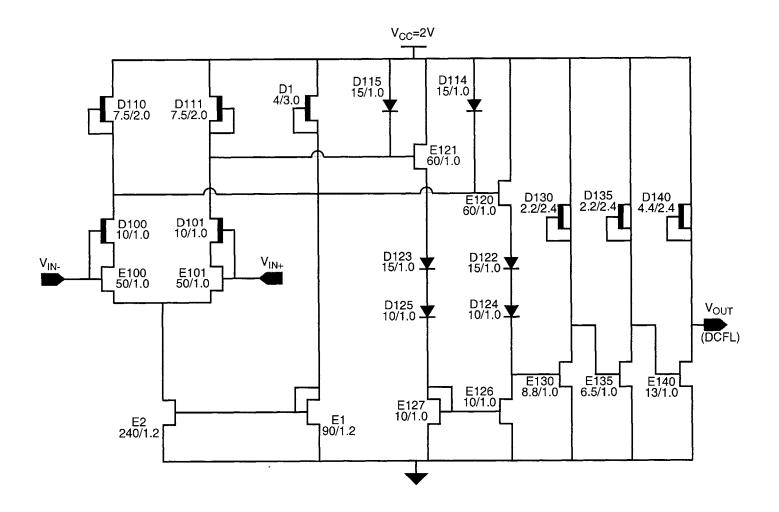

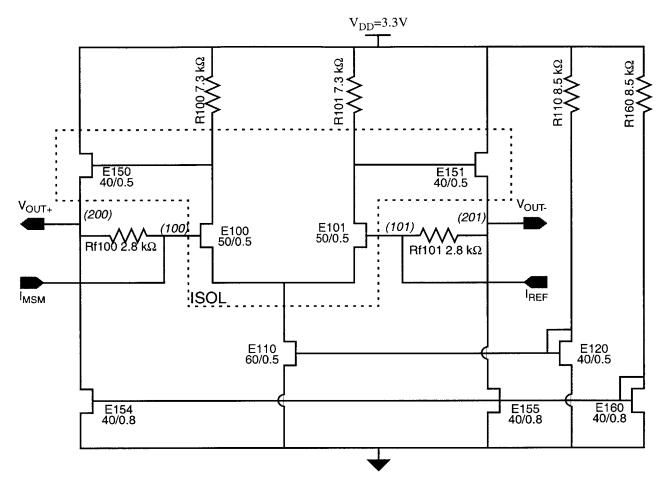

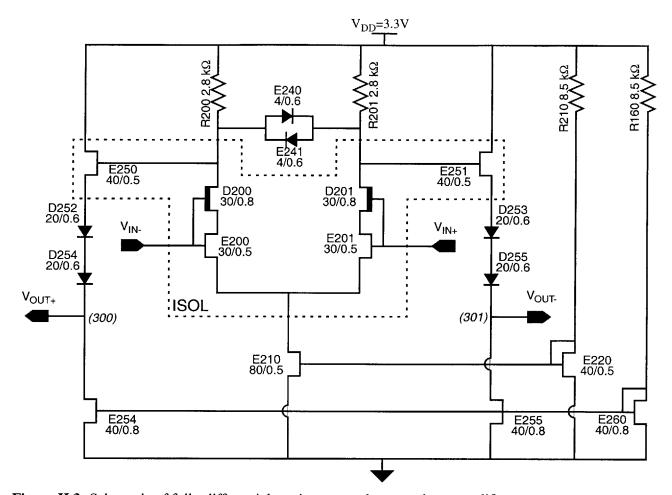

| 7.2  | Schematic of a low-power continuous time receiver                                                                                  |

| 7.3  | Simulated static characteristics of low power receiver                                                                             |

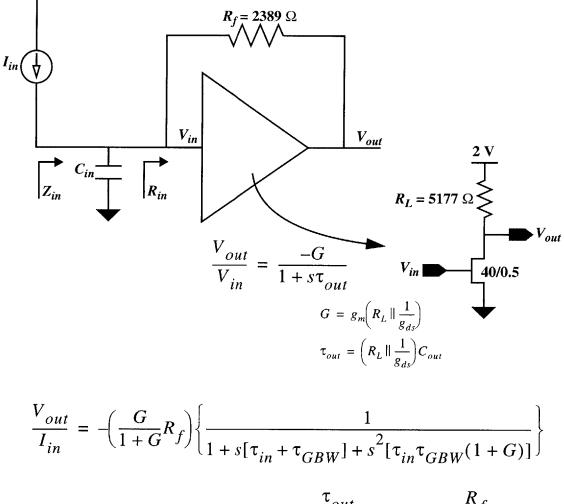

| 7.4  | Simplified analysis of transimpedance amplifier used as the first stage                                                            |

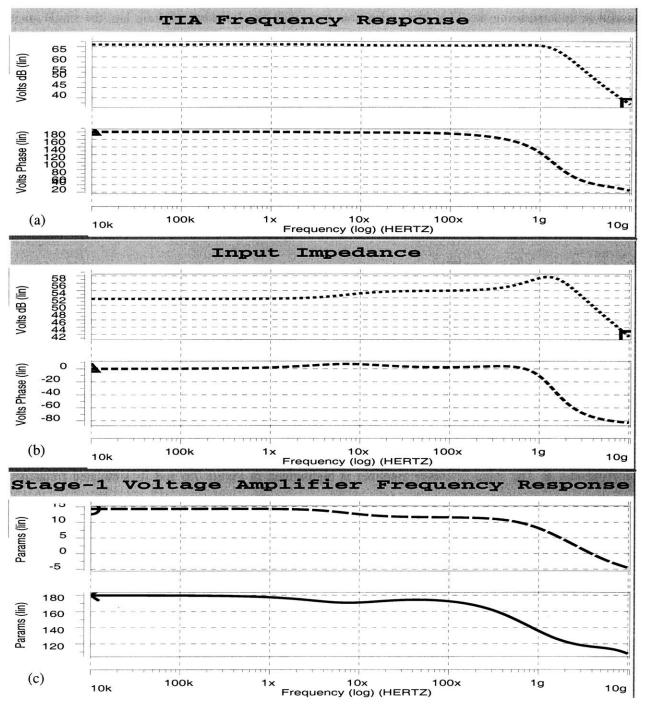

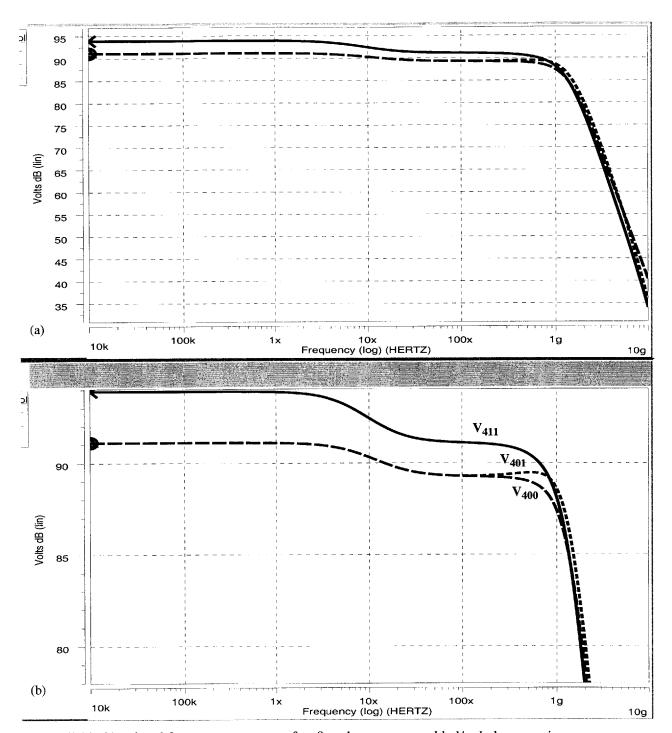

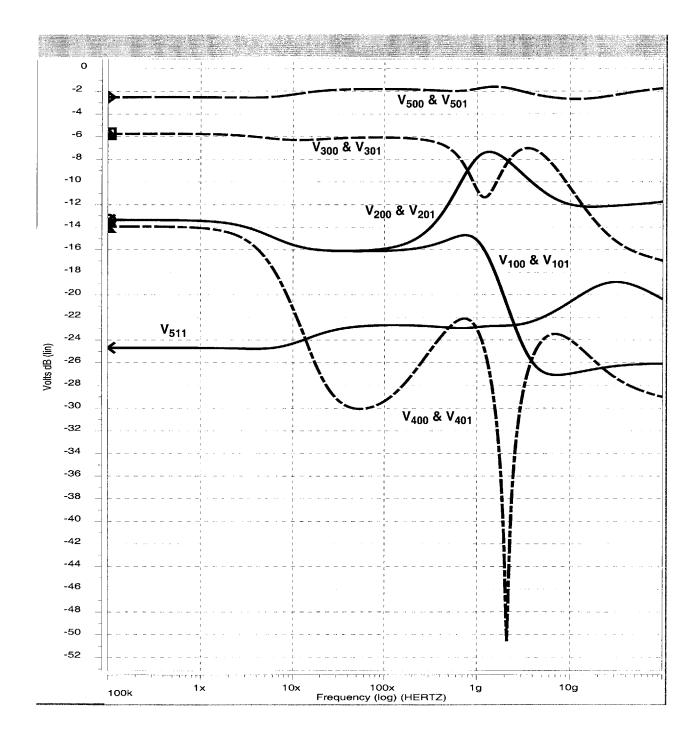

| 7.5  | Simulated frequency response of first stage of low power receiver                                                                  |

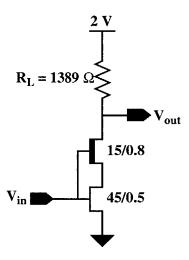

| 7.6  | Isolated schematic of the low power receiver's second stage voltage amplifier                                                      |

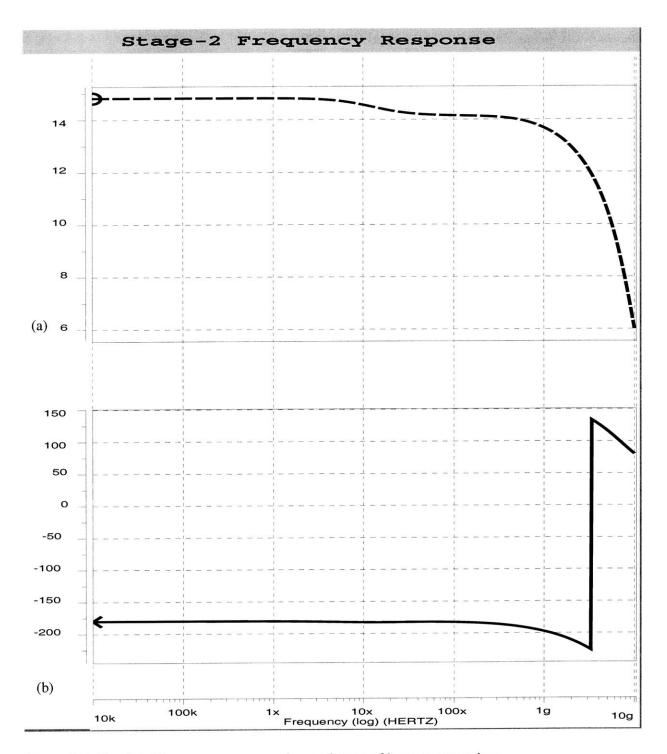

| 7.7  | Simulated frequency response of second stage of low power receiver                                                                 |

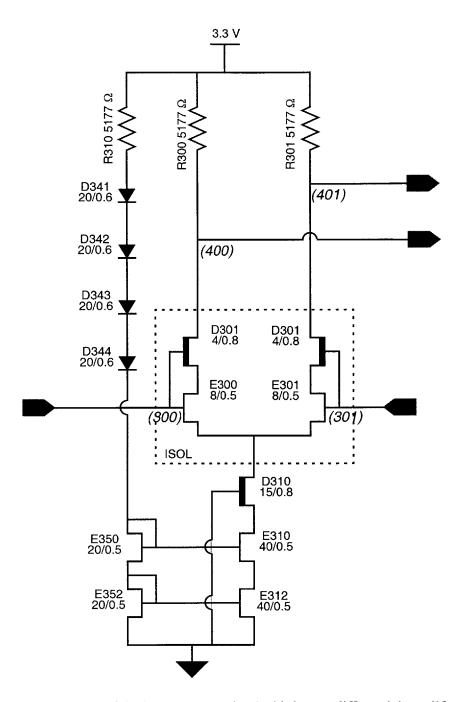

| 7.8  | Isolated schematic of the low power receiver's third stage differential amplifier                                                  |

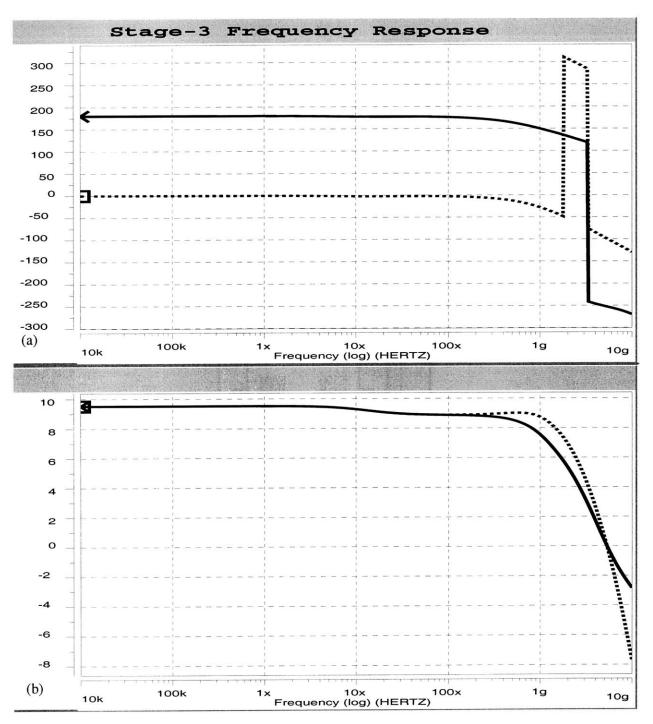

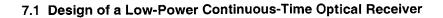

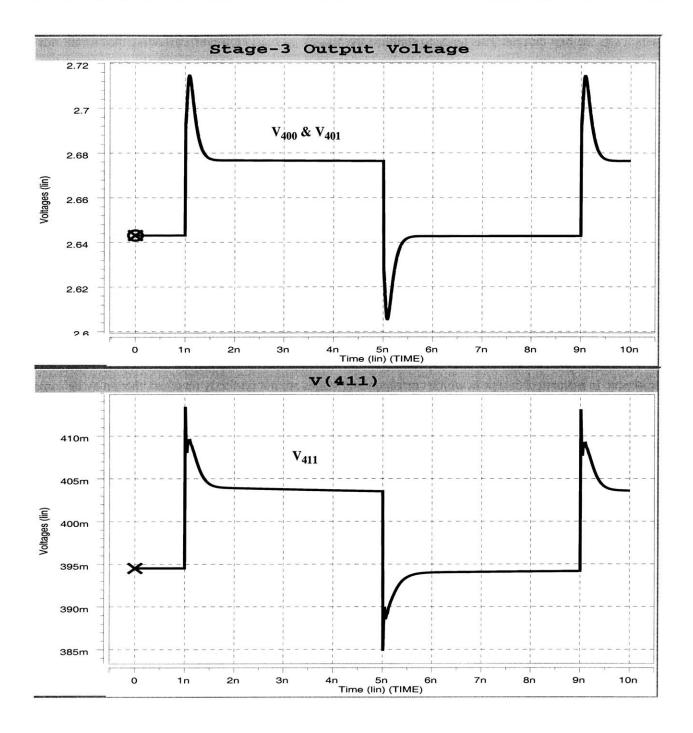

| 7.9  | Simulated frequency response of third stage of the low power receiver                                                              |

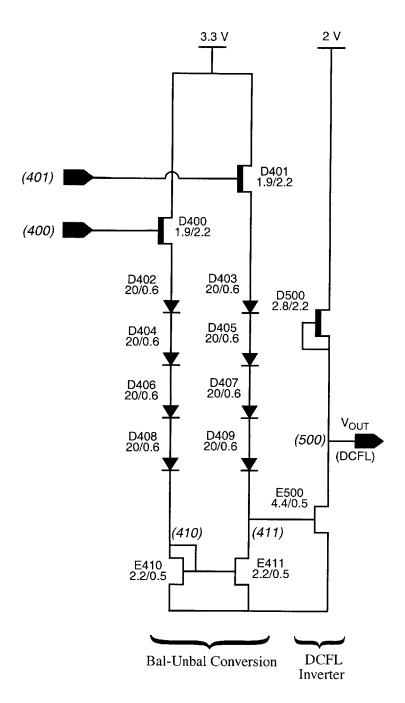

| 7.10 | Isolated schematic of balanced-to-unbalanced conversion circuit and DCFL inverter 352                                              |

| 7.11 | Simulated frequency response after first three stages and bal/unbal conversion                                                     |

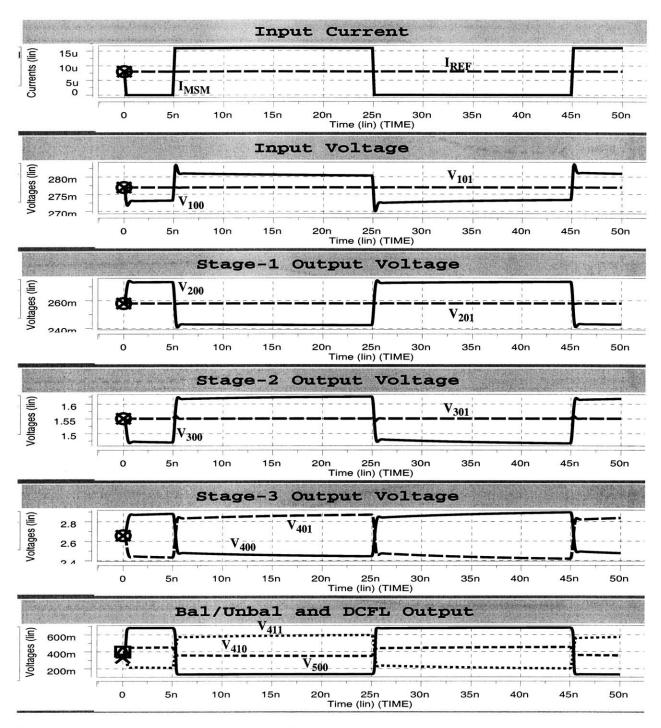

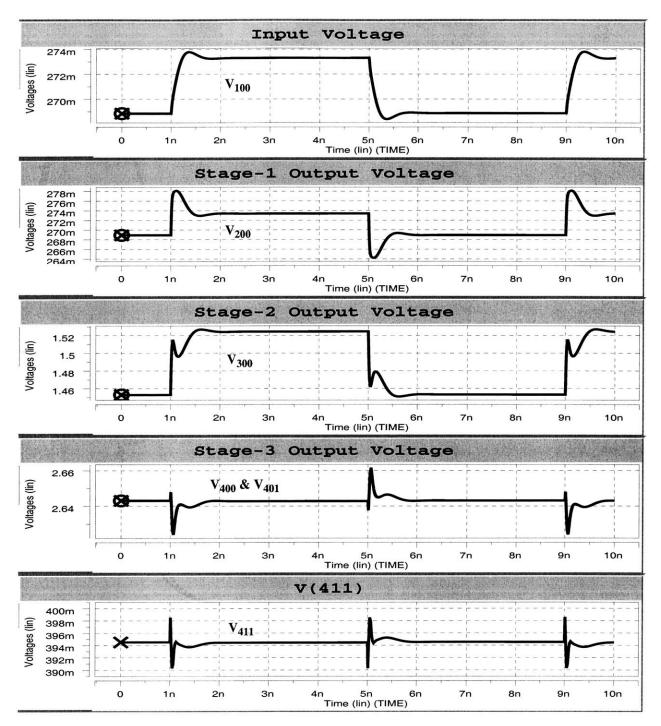

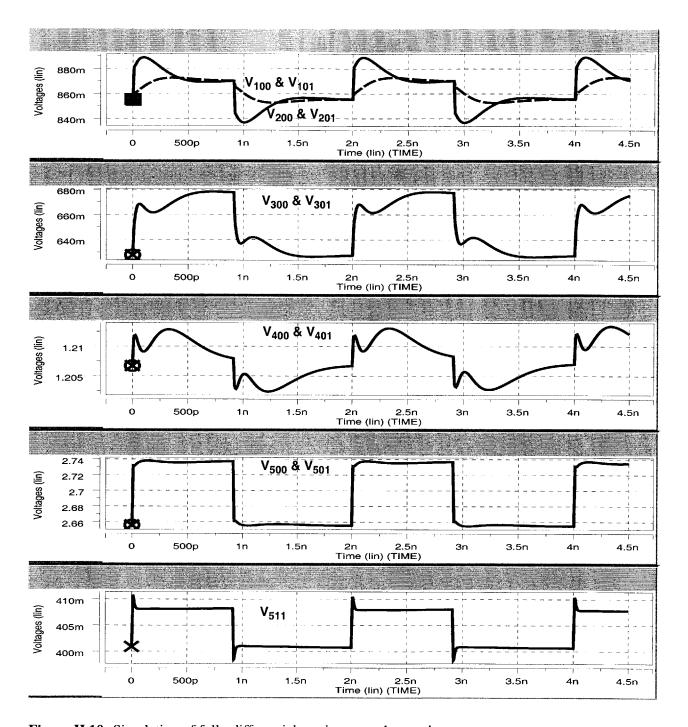

| 7.12 | Simulated transient response of the low power receiver                                                                             |

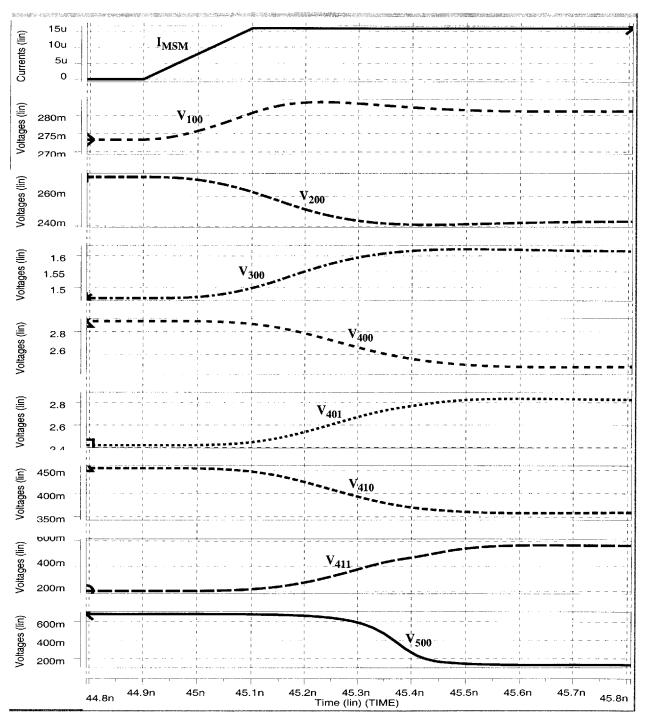

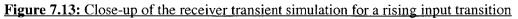

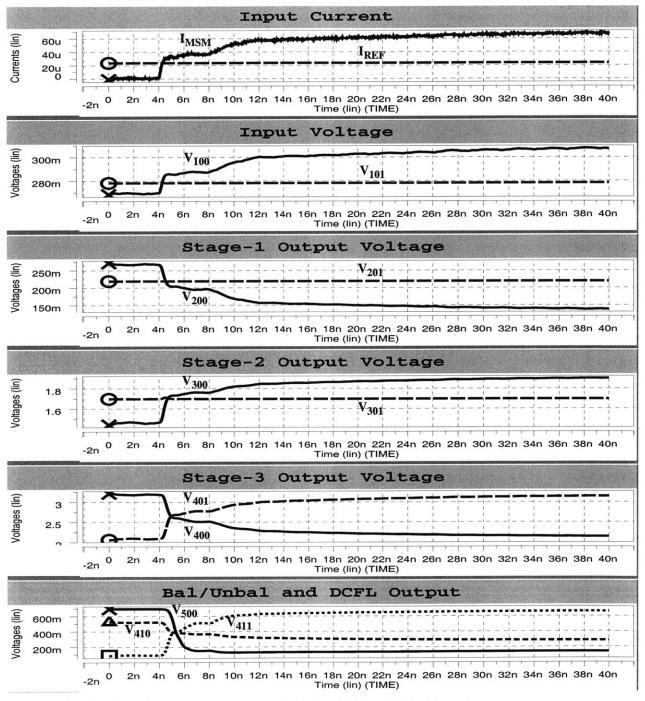

| 7.13 | Close-up of the receiver transient simulation for a rising input transition                                                        |

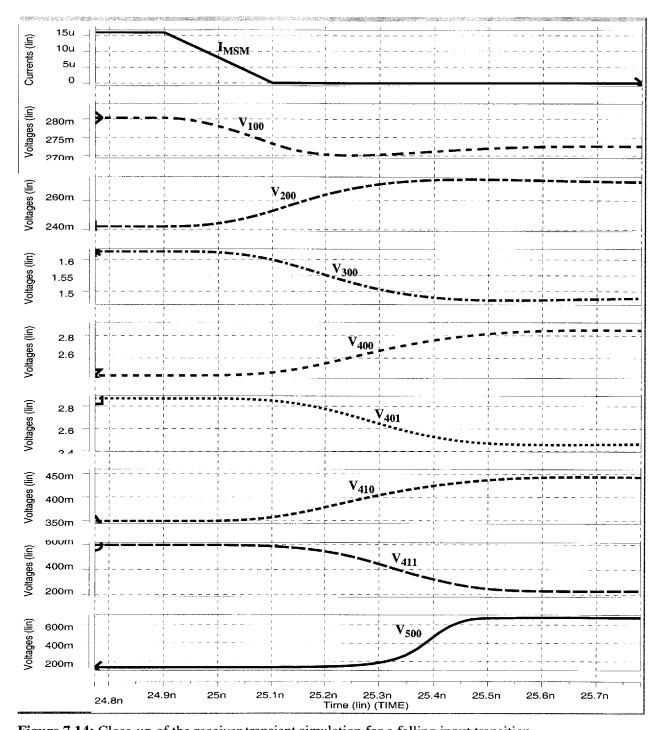

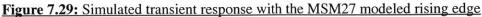

| 7.14 | Close-up of the receiver transient simulation for a falling input transition                                                       |

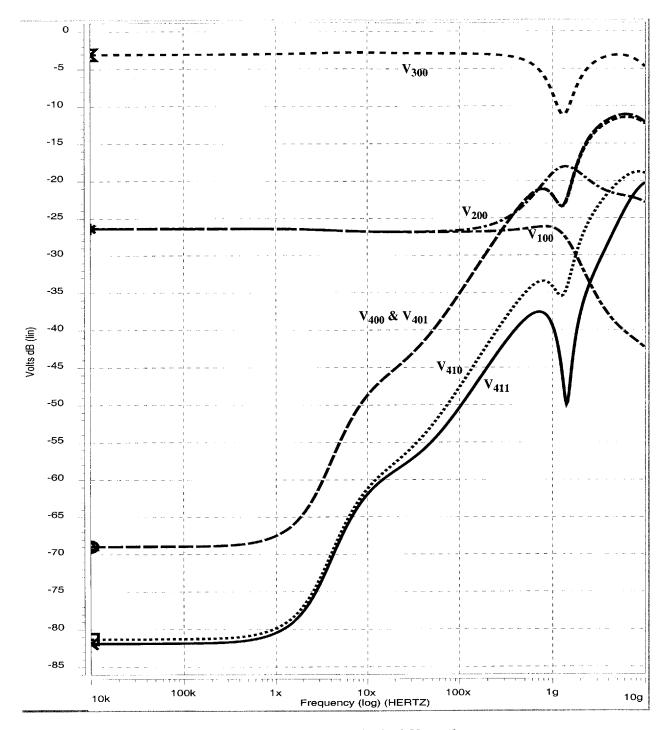

| 7.15                                                                                                 | Simulated frequency response to variations in the 2 V supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.16                                                                                                 | Simulated transient response to variations in the 2 V supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

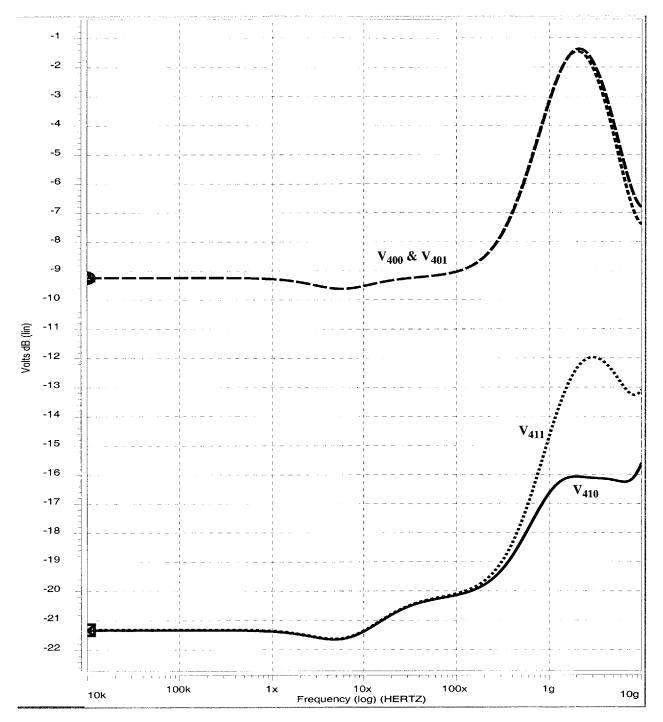

| 7.17                                                                                                 | Simulated frequency response to variations in the 3.3 V supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7.18                                                                                                 | Simulated transient response to variations in the 3.3 V supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

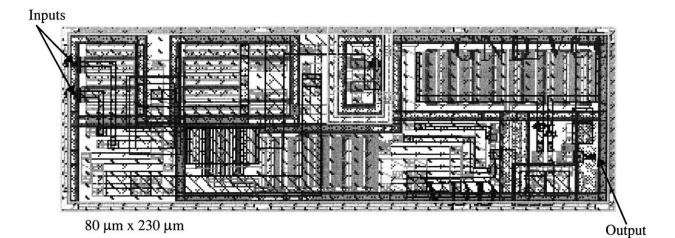

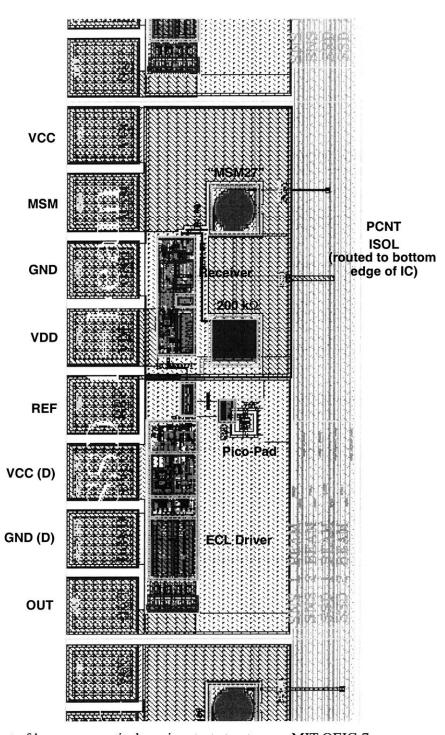

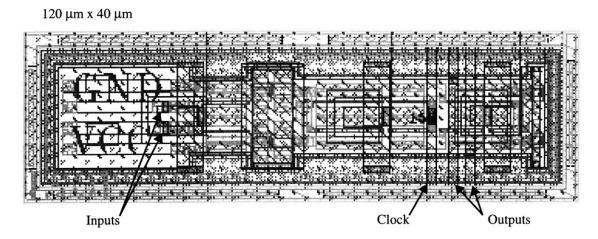

| 7.19                                                                                                 | Layout plot of low power receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

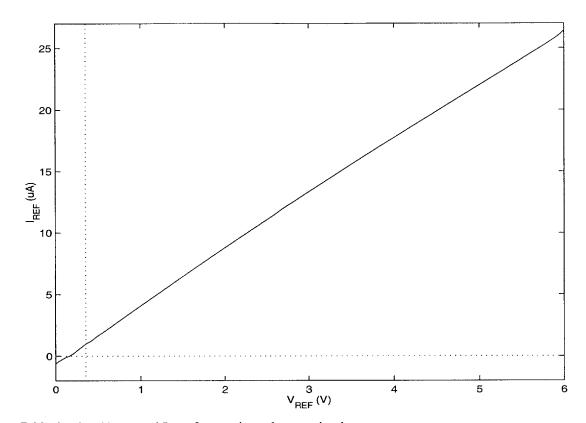

| 7.20                                                                                                 | Setting VREF and IREF for receiver characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

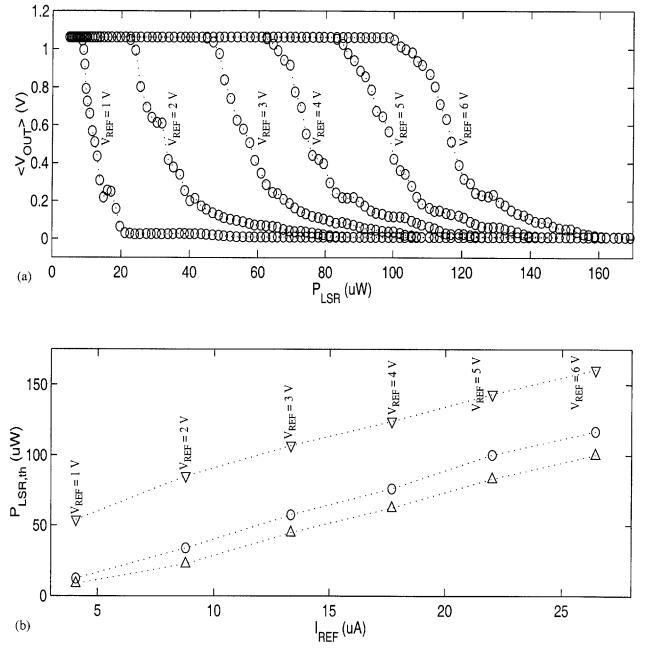

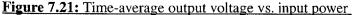

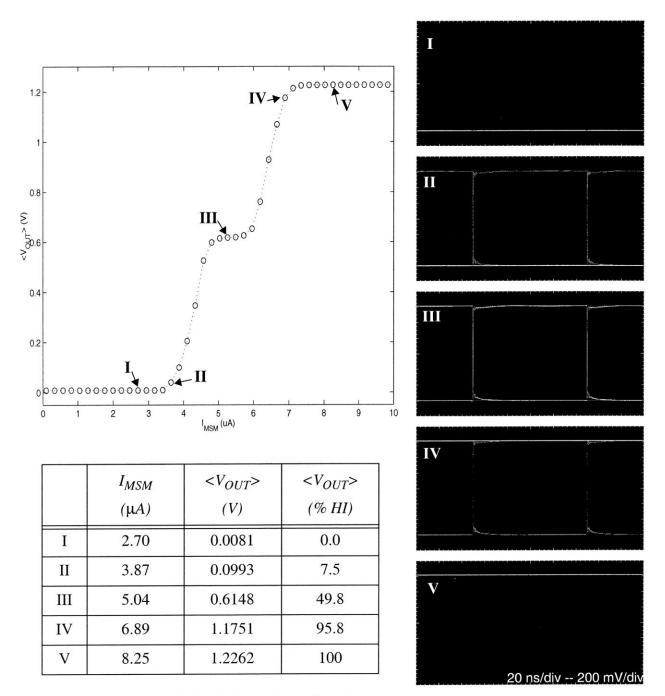

| 7.21                                                                                                 | Time-average output voltage vs. input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

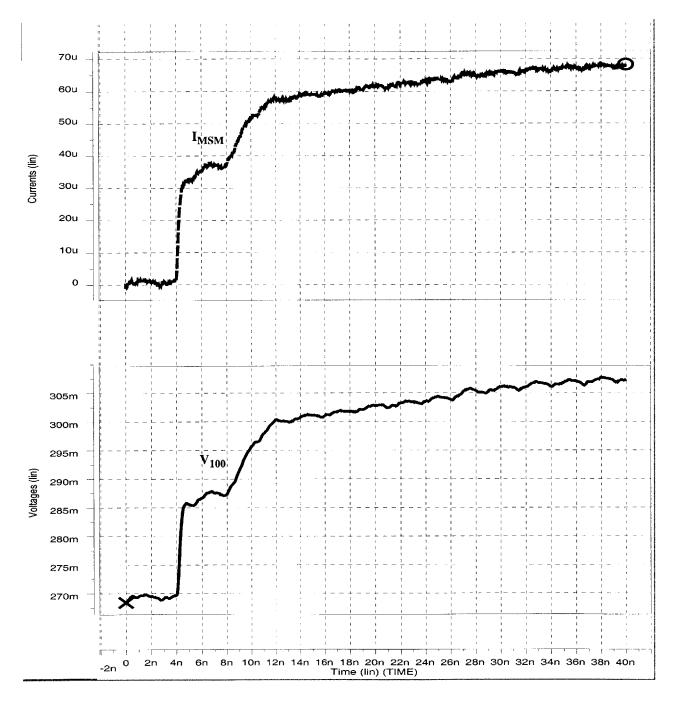

| 7.22                                                                                                 | Transient simulation of receiver input with the MSM27 modeled rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

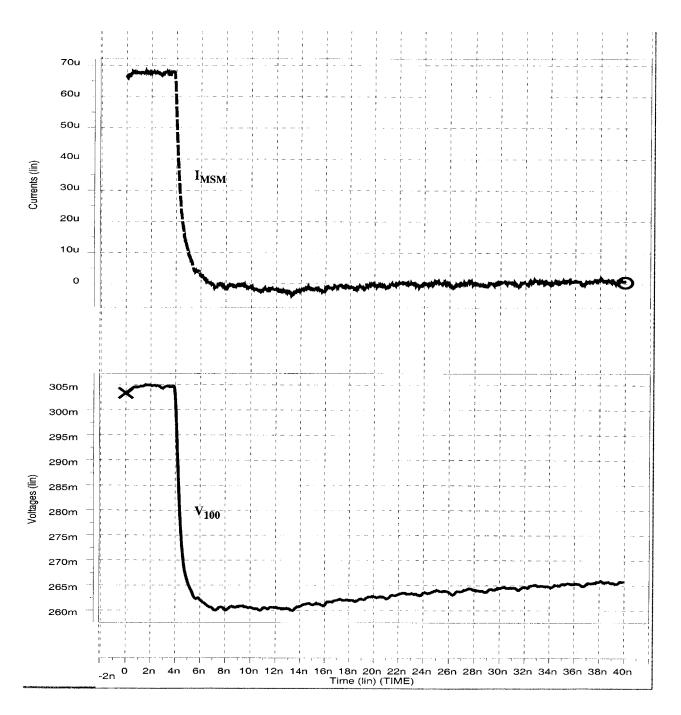

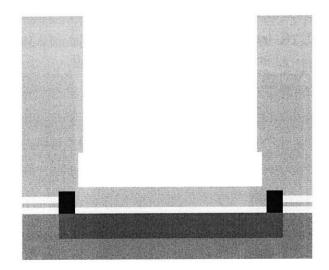

| 7.23                                                                                                 | Transient simulation of receiver input with the MSM27 modeled falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

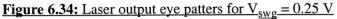

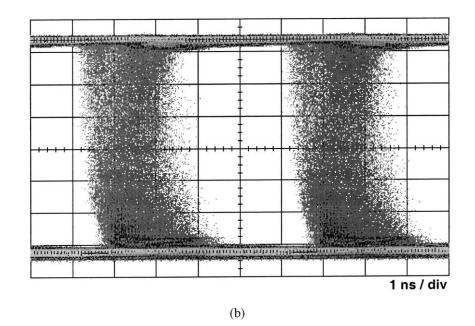

| 7.24                                                                                                 | Eye pattern of optical signal used to test the receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

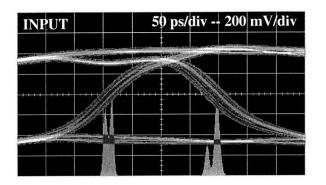

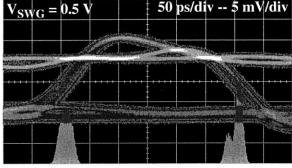

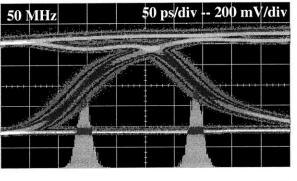

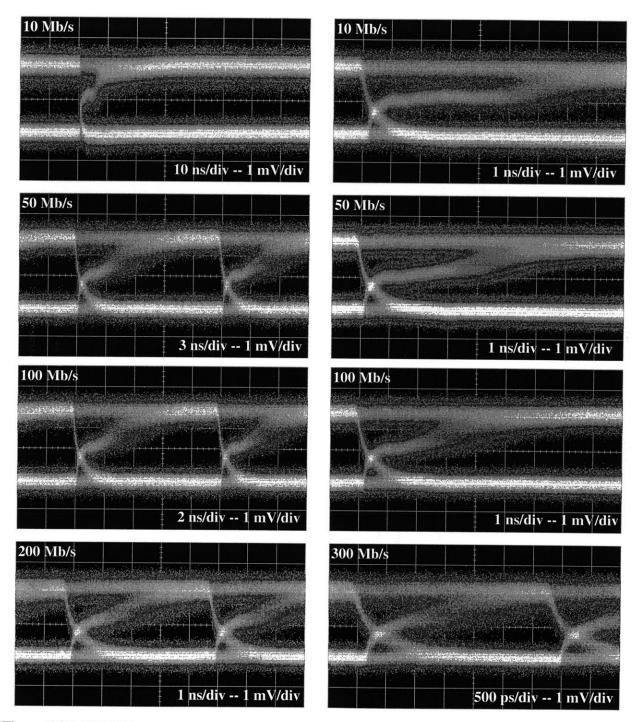

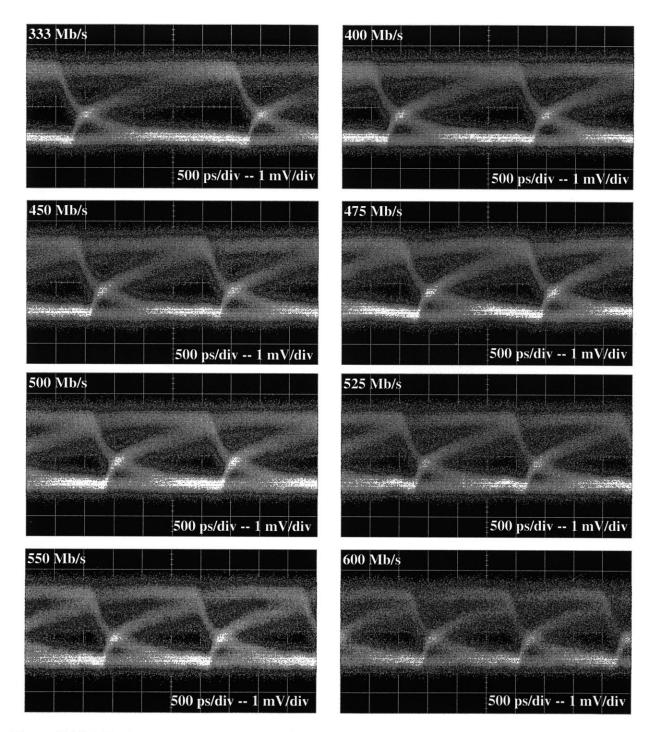

| 7.25                                                                                                 | MSM27 source current eye patterns 1 of 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

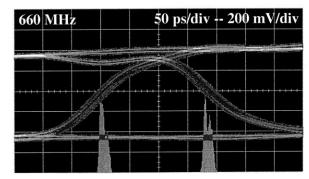

| 7.26                                                                                                 | MSM27 source current eye patterns 2 of 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

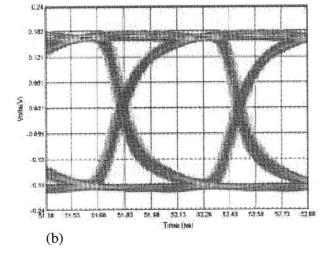

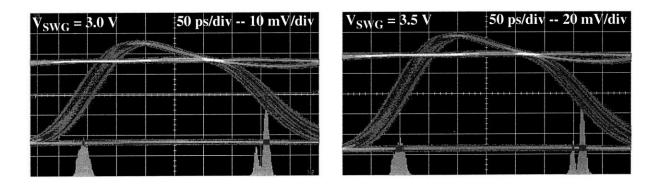

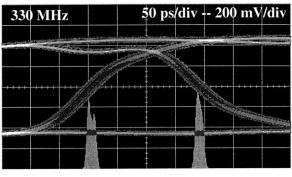

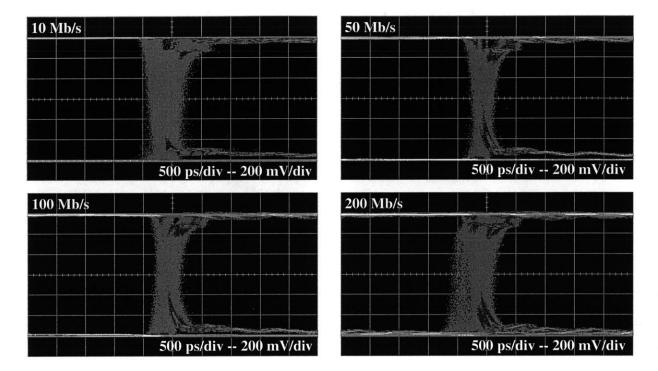

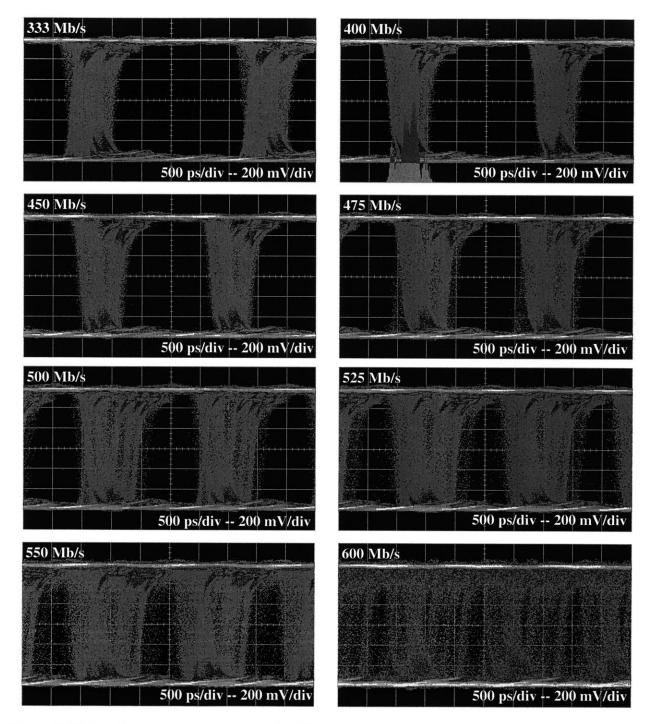

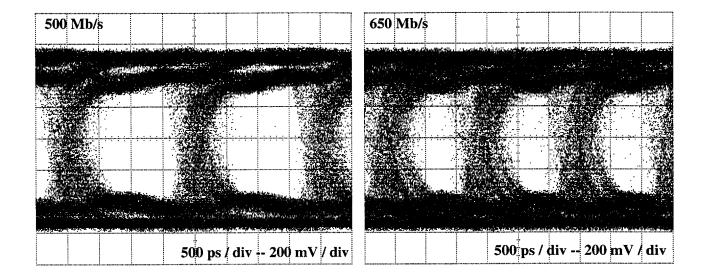

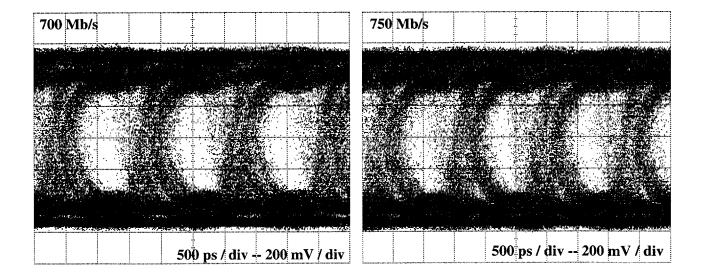

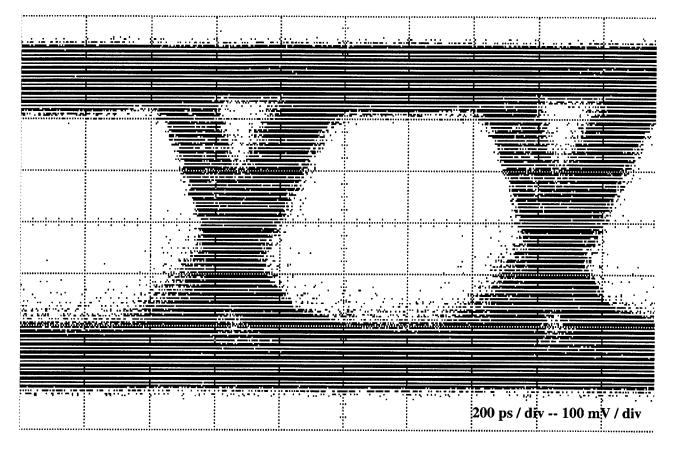

| 7.27                                                                                                 | Receiver output eye patterns 1 of 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

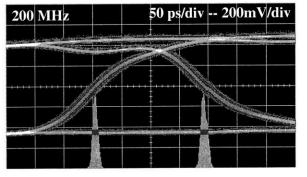

| 7.28                                                                                                 | Receiver output eye patterns 2 of 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.29                                                                                                 | Simulated transient response with the MSM27 modeled rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.30                                                                                                 | Simulated transient response with the MSM27 modeled falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

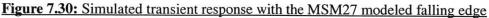

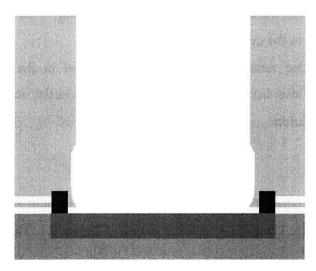

| A.1                                                                                                  | HGaAs3 Process Flow Schematic through Metal 1 [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

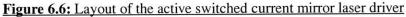

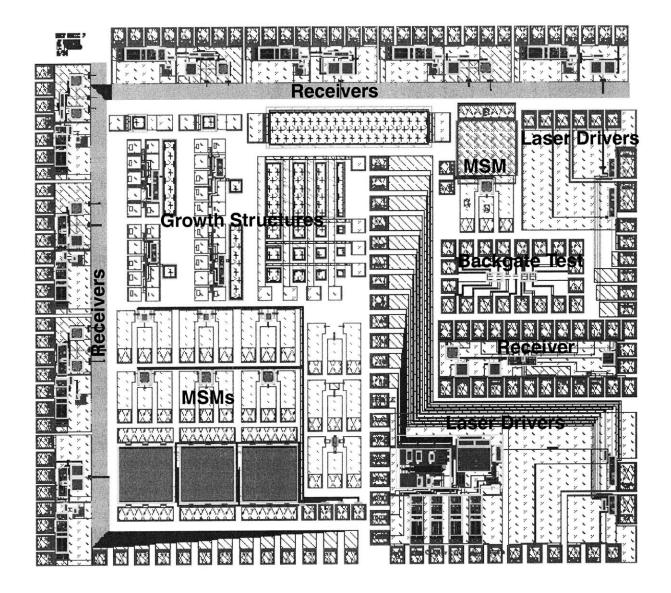

| C.1                                                                                                  | Layout MIT-OEIC-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C.1<br>C.2                                                                                           | Layout MIT-OEIC-7       404         Layout of die cut from MIT-OEIC-7 for laser driver characterization       405                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

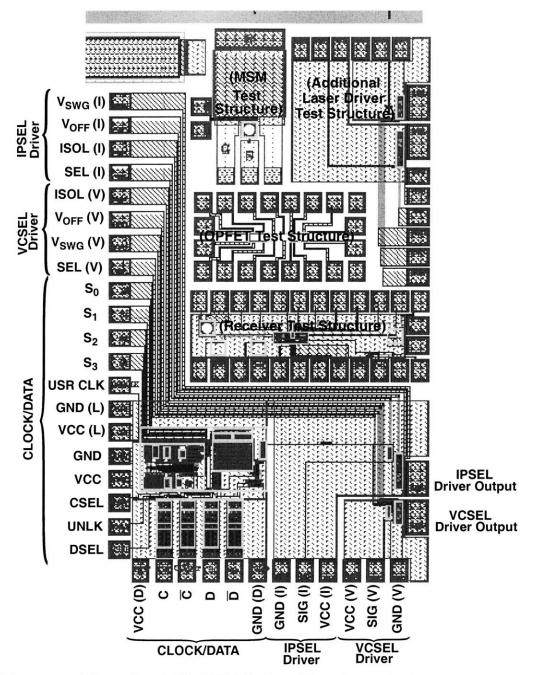

| C.2                                                                                                  | Layout of die cut from MIT-OEIC-7 for laser driver characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

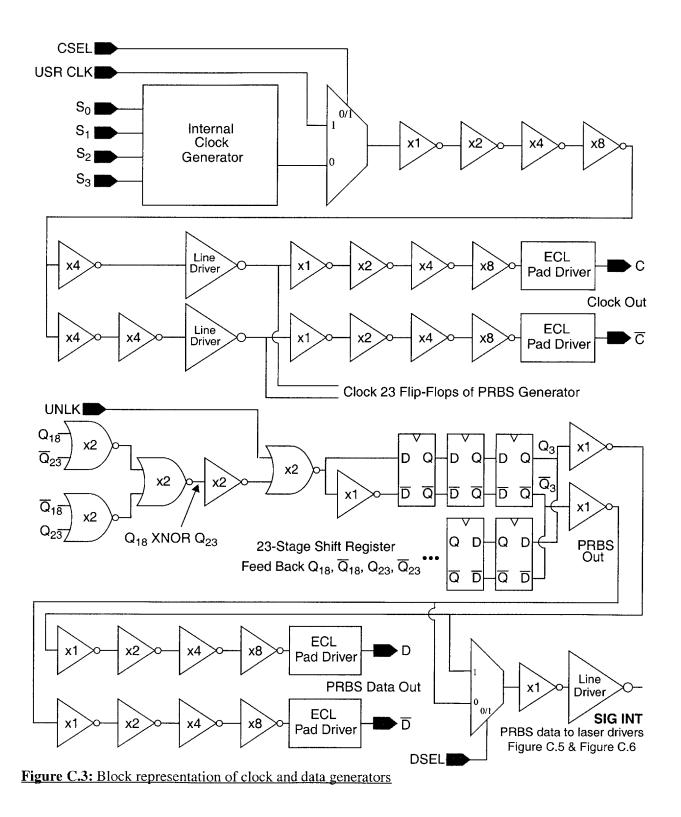

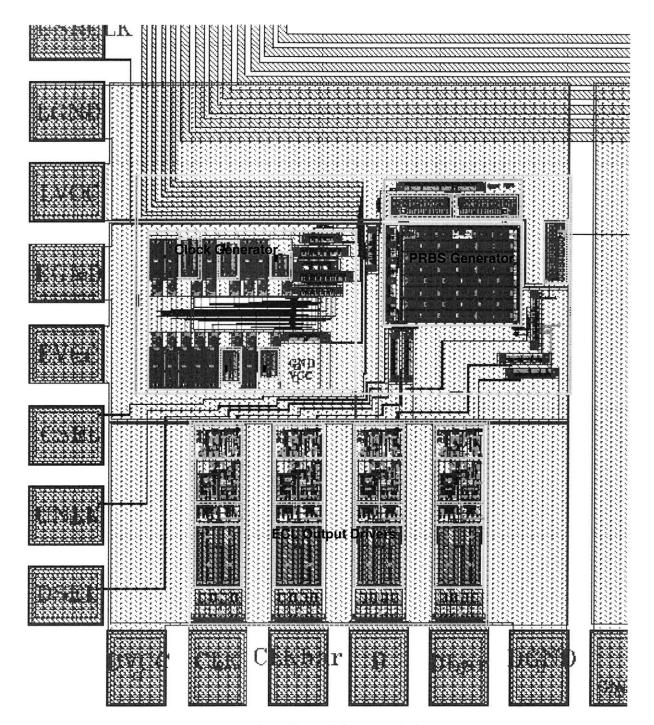

| C.2<br>C.3                                                                                           | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C.2<br>C.3<br>C.4                                                                                    | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

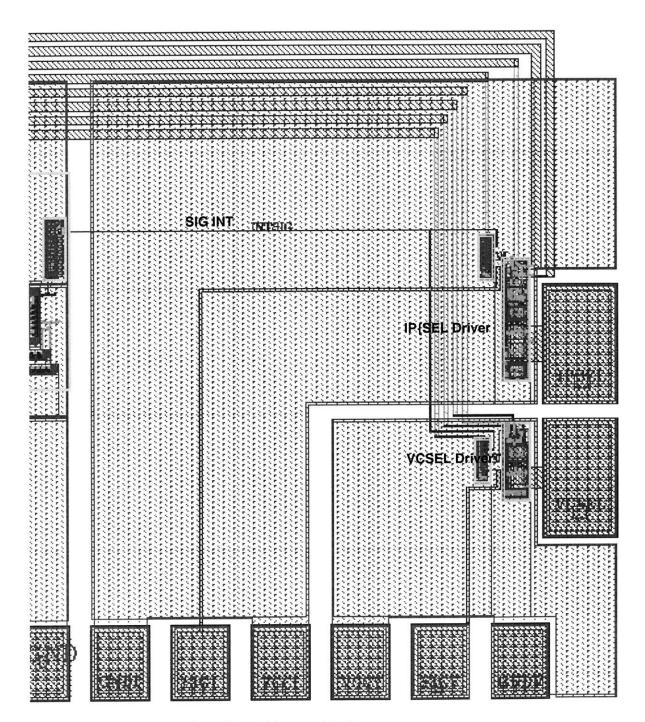

| C.2<br>C.3<br>C.4<br>C.5                                                                             | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

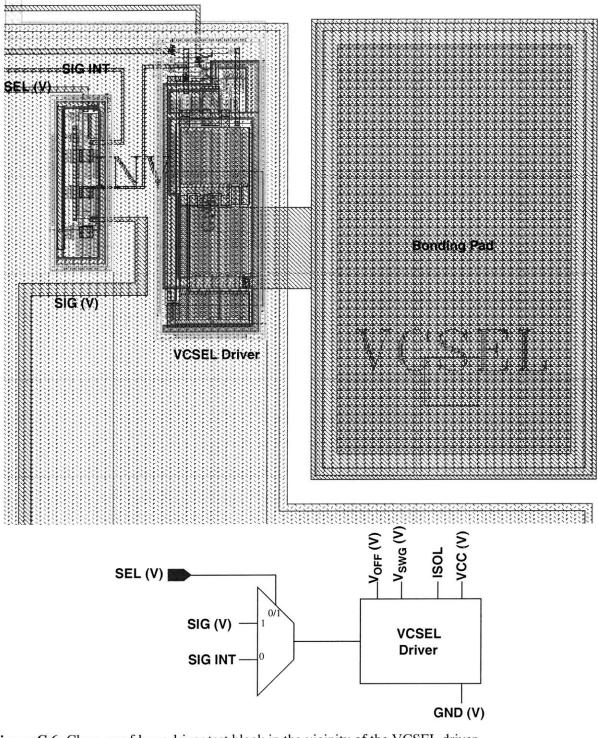

| C.2<br>C.3<br>C.4<br>C.5<br>C.6                                                                      | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7                                                               | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization415Bonding diagram for laser driver + VCSEL characterization416                                                                                                                                                                                                                                                                                 |

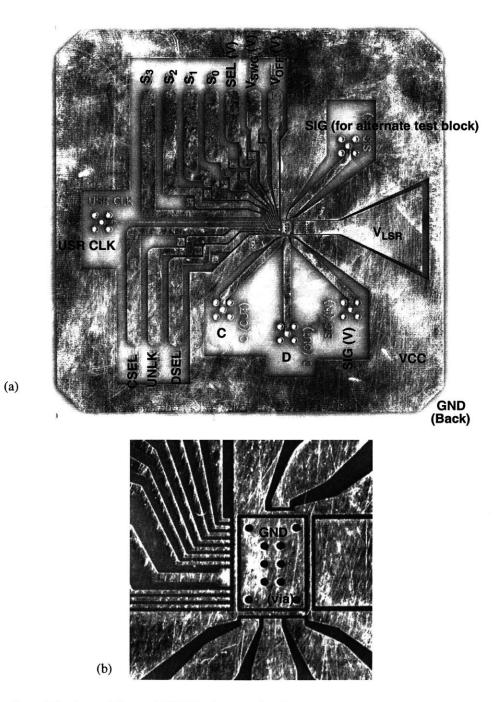

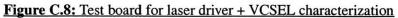

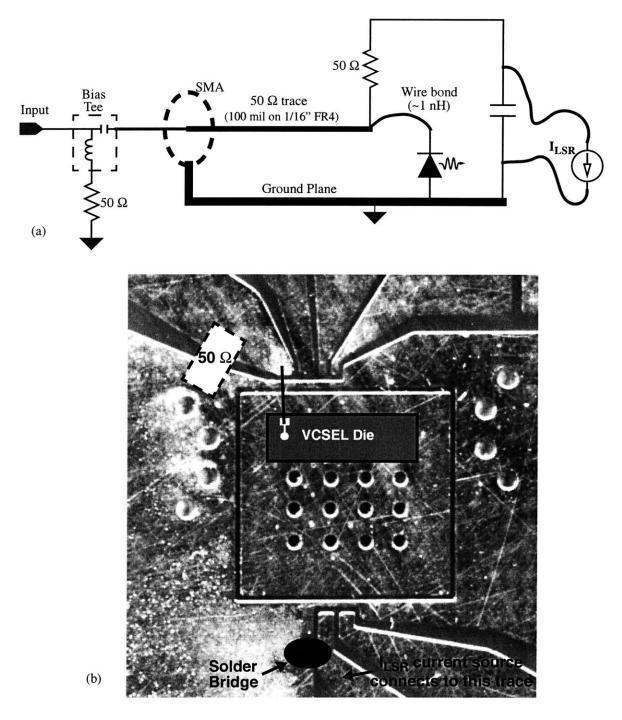

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8                                                        | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization415                                                                                                                                                                                                                                                                                                                                             |

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10                                         | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization415Bonding diagram for laser driver + VCSEL characterization416                                                                                                                                                                                                                                                                                 |

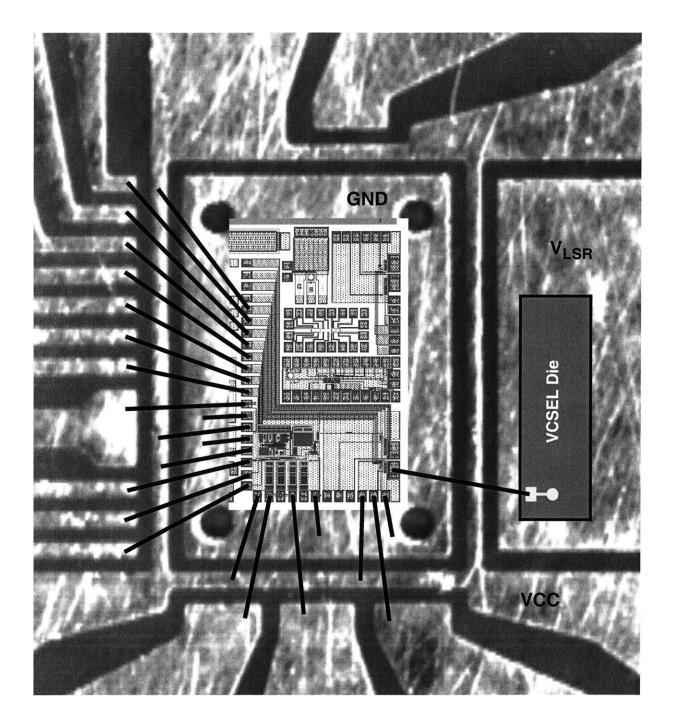

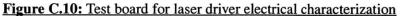

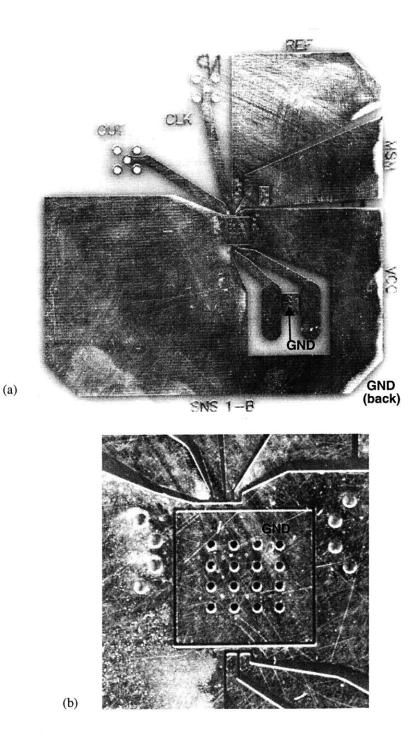

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11                                 | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization416Test board for laser driver electrical characterization417                                                                                                                                                                                                                                                                                   |

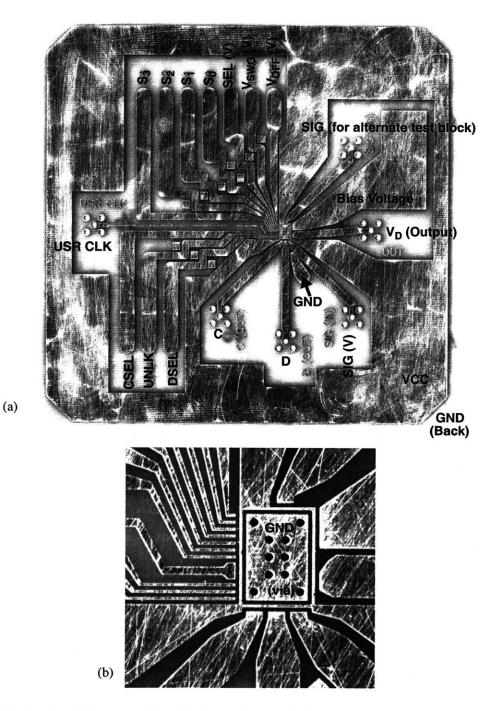

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12                         | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization416Test board for laser driver electrical characterization417Bonding diagram for laser driver electrical characterization418                                                                                                                                                                                                                    |

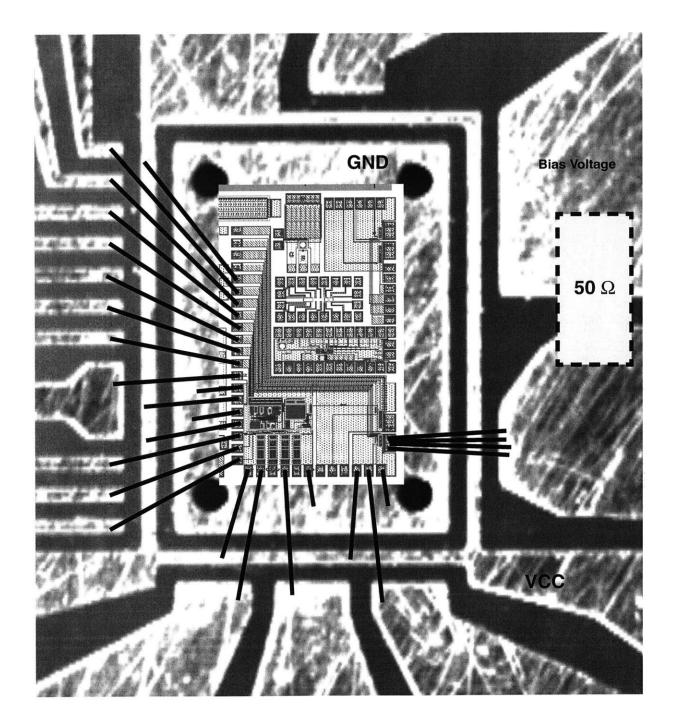

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12<br>C.13                 | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit.412Test board for laser driver + VCSEL characterization416Test board for laser driver electrical characterization417Bonding diagram for laser driver electrical characterization418Laser module test board420Laser module construction and schematic421Layout of low power optical receiver test structure on MIT-OEIC-7423                                                                           |

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12<br>C.13                 | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization416Test board for laser driver electrical characterization417Bonding diagram for laser driver electrical characterization418Laser module test board420Laser module construction and schematic421Layout of low power optical receiver test structure on MIT-OEIC-7423Block diagram of low power optical receiver test structure on MIT-OEIC-7424 |

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12<br>C.13<br>C.14         | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit.412Test board for laser driver + VCSEL characterization416Test board for laser driver electrical characterization417Bonding diagram for laser driver electrical characterization418Laser module test board420Laser module construction and schematic421Layout of low power optical receiver test structure on MIT-OEIC-7423                                                                           |

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12<br>C.13<br>C.14<br>C.15 | Layout of die cut from MIT-OEIC-7 for laser driver characterization405Block representation of clock and data generators408Clock and data generator portion of laser driver test block409Laser driver portion of laser driver test block410Close up of laser driver test block in the vicinity of the VCSEL driver411Schematic of line driver circuit412Test board for laser driver + VCSEL characterization416Test board for laser driver electrical characterization417Bonding diagram for laser driver electrical characterization418Laser module test board420Laser module construction and schematic421Layout of low power optical receiver test structure on MIT-OEIC-7423Block diagram of low power optical receiver test structure on MIT-OEIC-7424 |

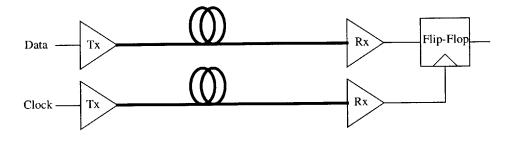

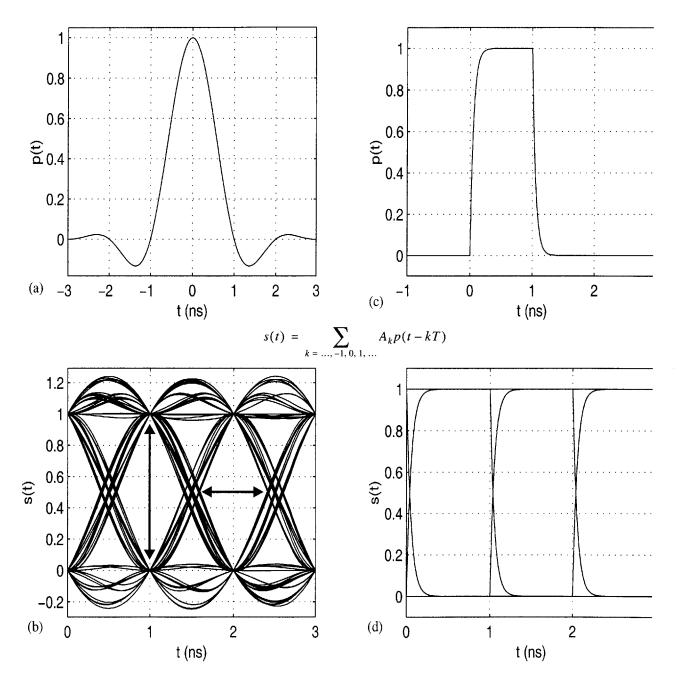

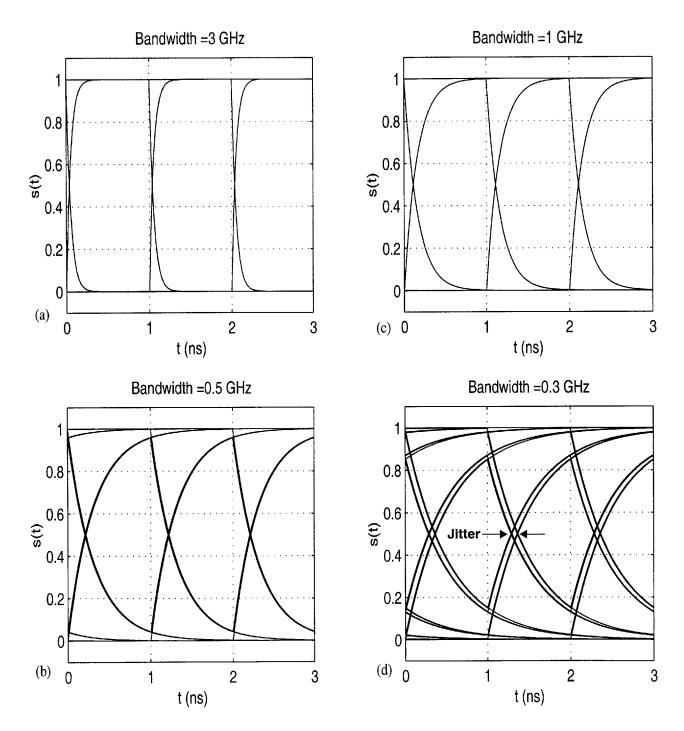

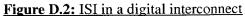

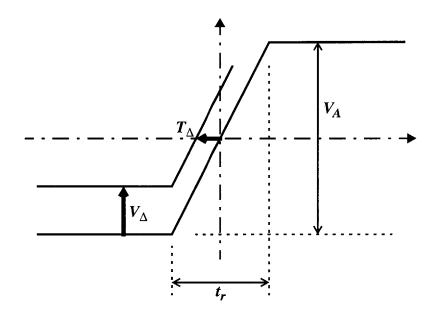

| D.1<br>D.2<br>D.3                             | Pulse shapes and data signals in communication links and digital interconnects                                                                                                                                                                                                                                             |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

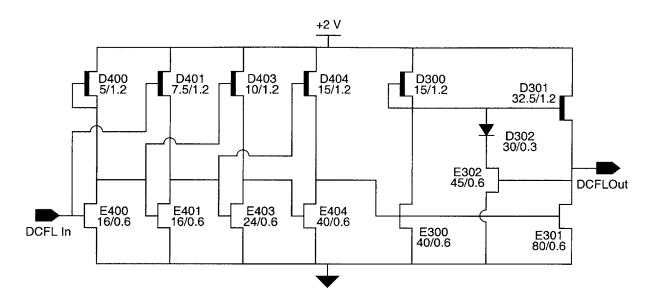

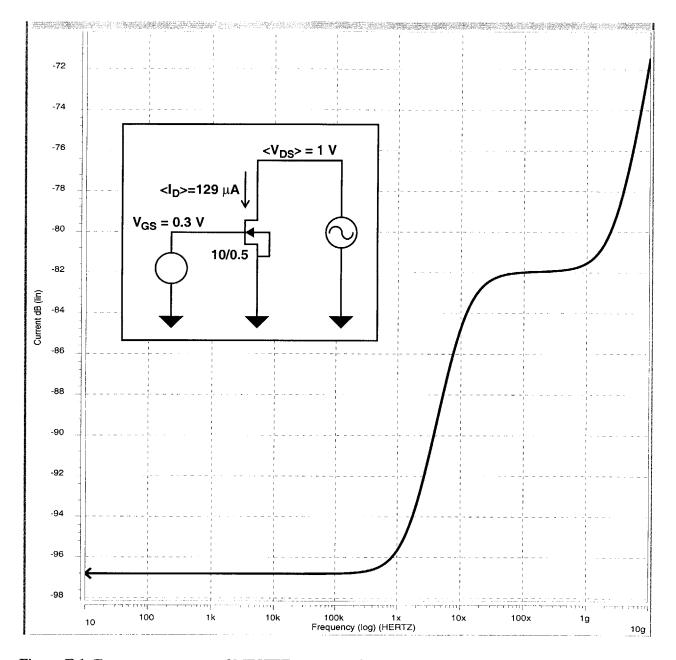

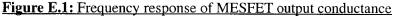

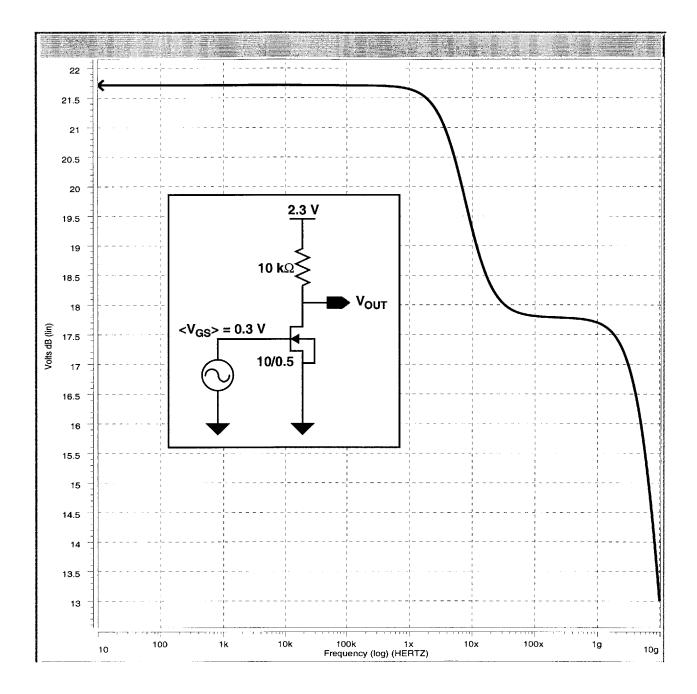

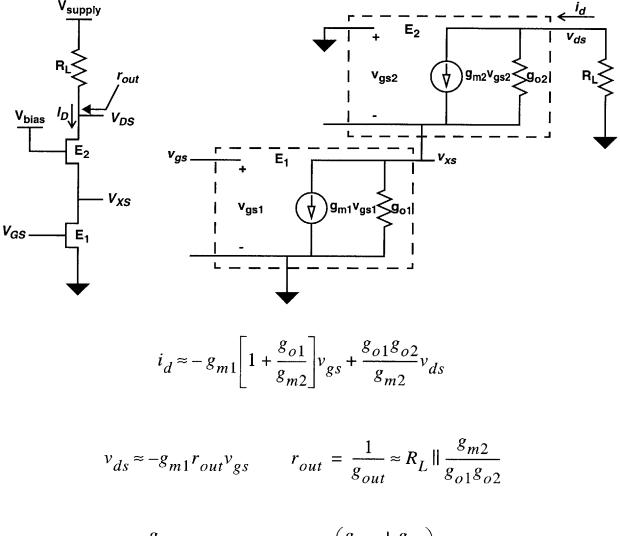

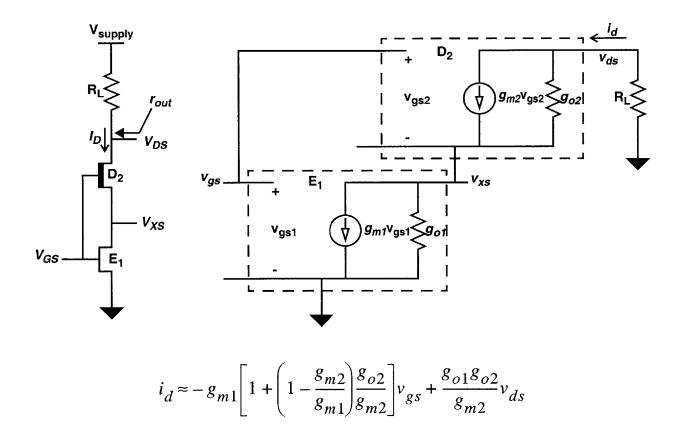

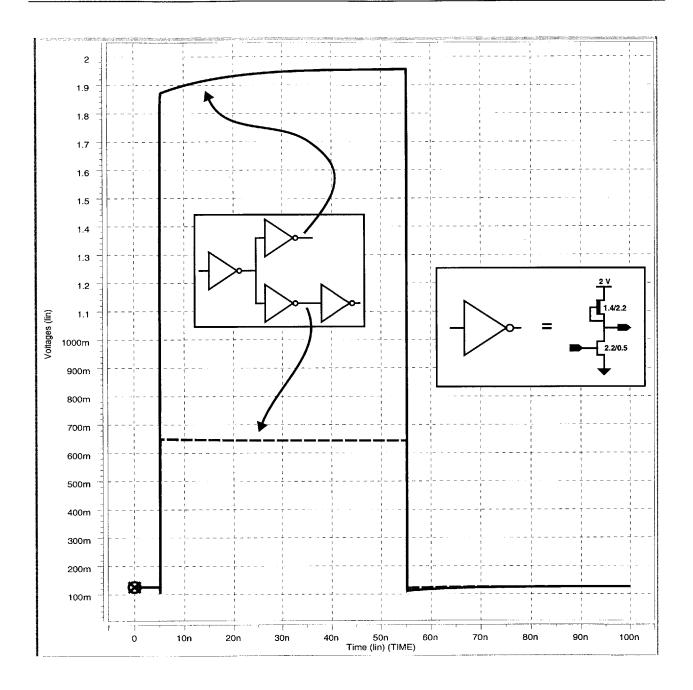

| E.1<br>E.2<br>E.3<br>E.4<br>E.5<br>E.6<br>E.7 | Frequency response of MESFET output conductance436Frequency response of common-source amplifier437Step response of common-source amplifier438A simple model for drain-lag440A common-source amplifier using a cascode442A common-source amplifier using an "active" cascode443Clamping controls drain lag in DCFL logic445 |

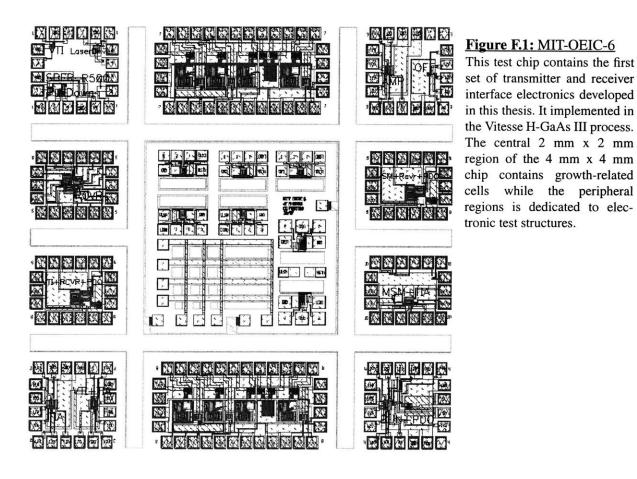

| F.1                                           | MIT-OEIC-6                                                                                                                                                                                                                                                                                                                 |

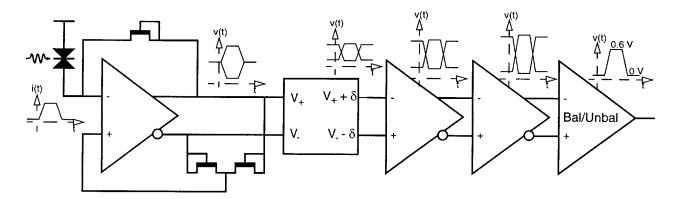

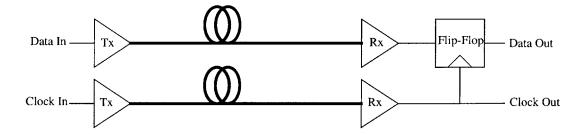

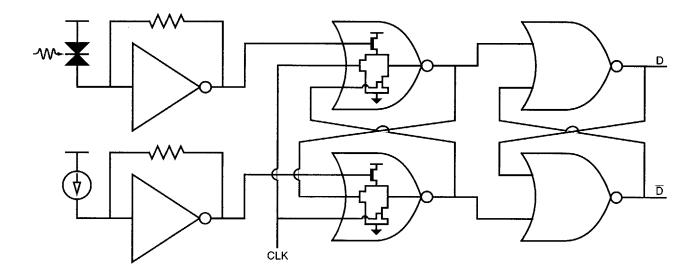

| F.2                                           | First generation optical receiver: block diagram                                                                                                                                                                                                                                                                           |

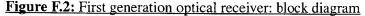

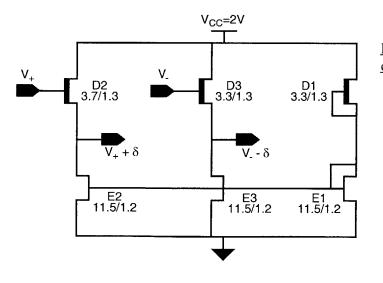

| F.3                                           | Schematic of first generation optical receiver: first-stage TIA                                                                                                                                                                                                                                                            |

| F.4                                           | Schematic of first generation optical receiver: differential offset stage                                                                                                                                                                                                                                                  |

| F.5                                           | Schematic of first generation optical receiver: second gain stage                                                                                                                                                                                                                                                          |

| F.6                                           | Schematic of first generation optical receiver: third gain stage and conversion to DCFL output 452                                                                                                                                                                                                                         |

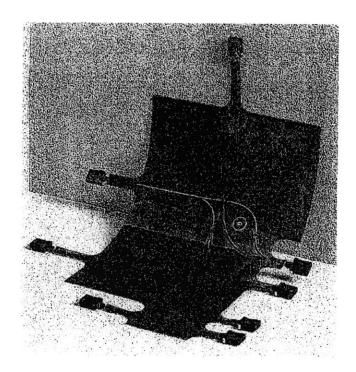

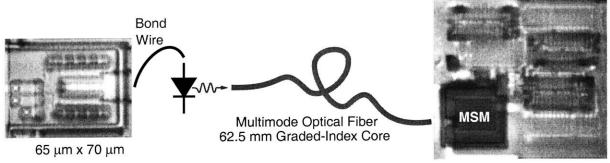

| F.7                                           | First generation optical link demonstration                                                                                                                                                                                                                                                                                |

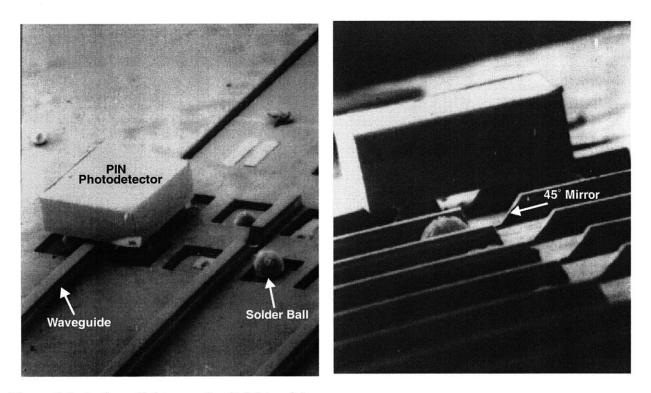

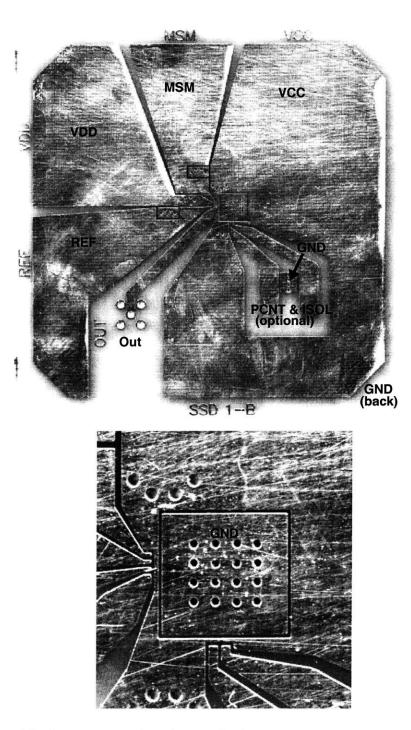

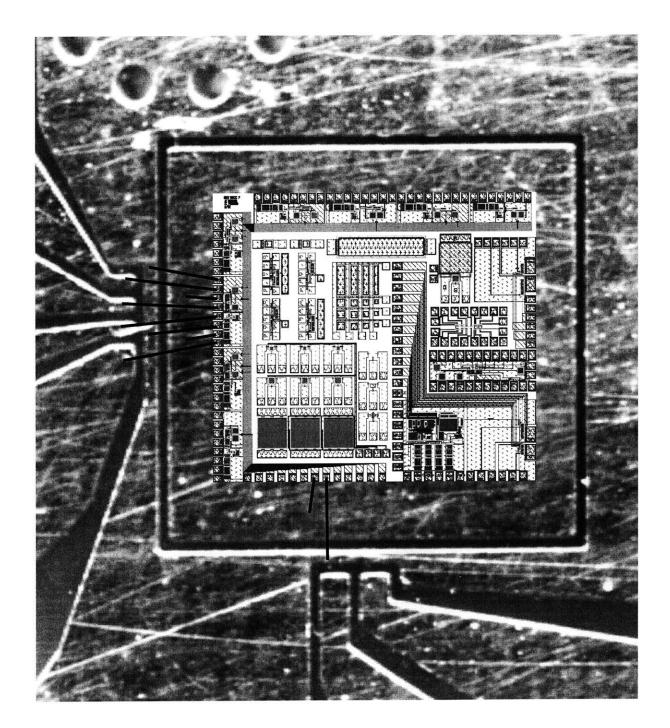

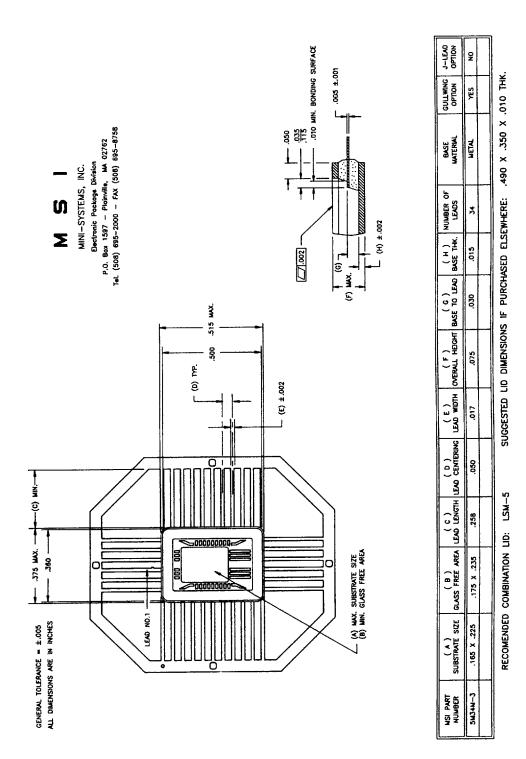

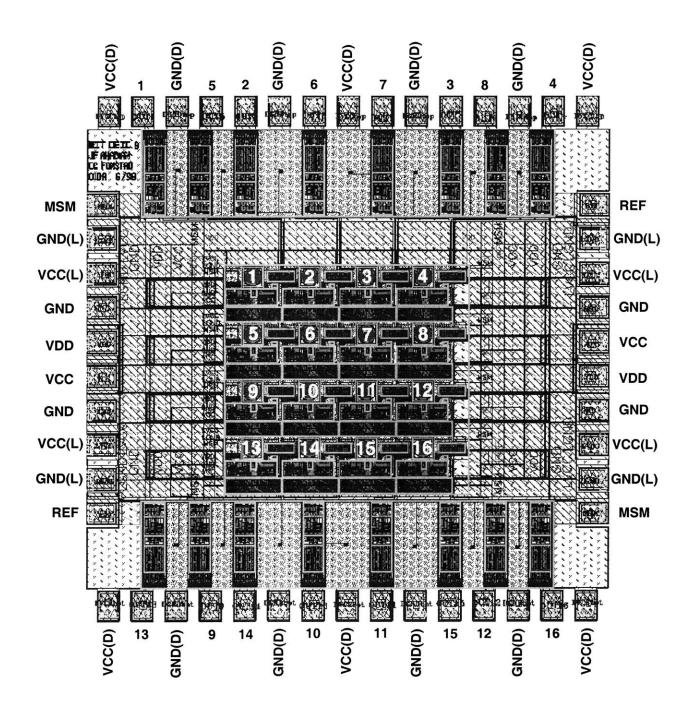

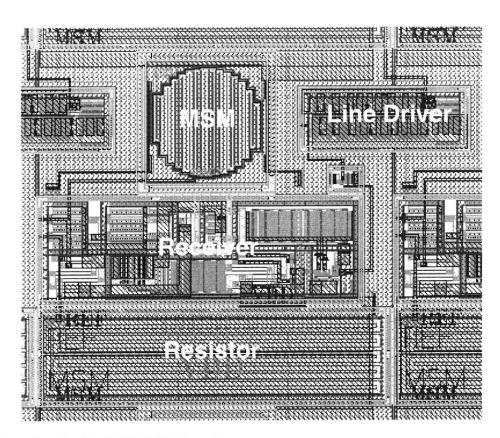

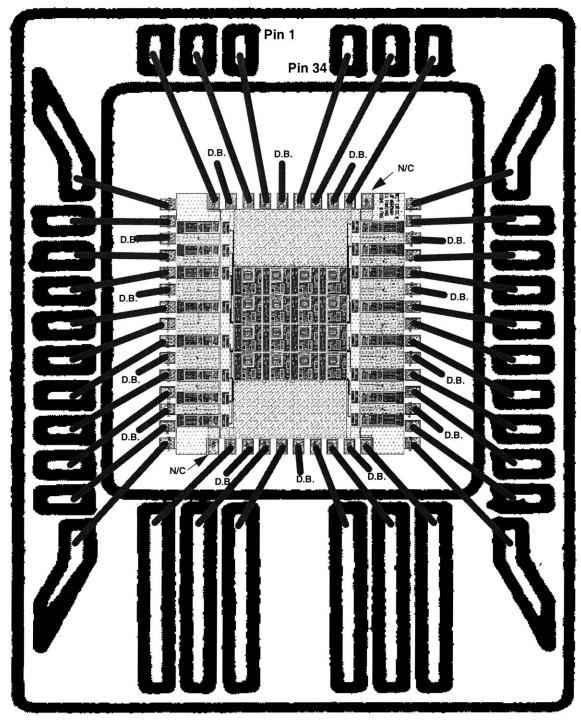

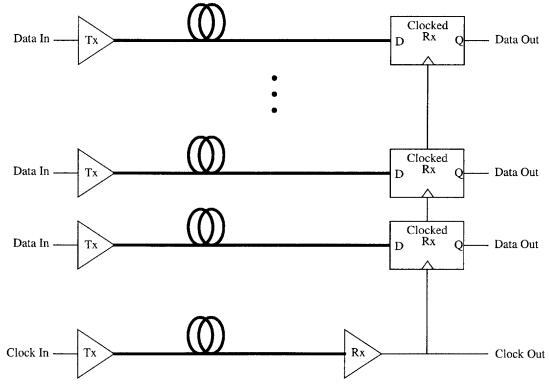

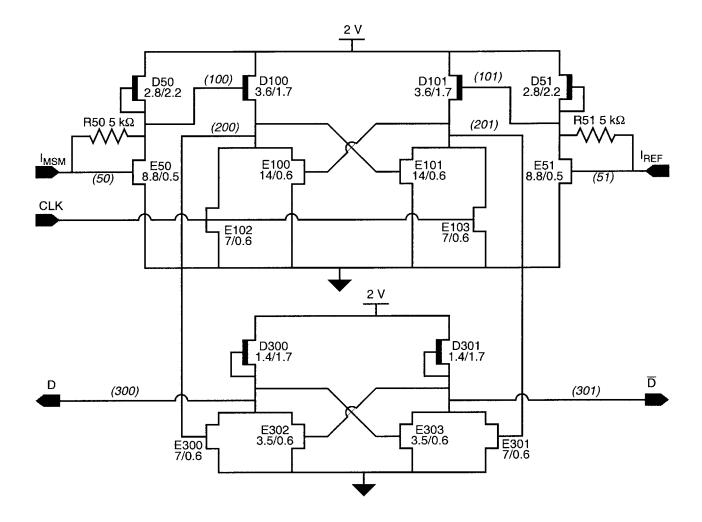

| G.1<br>G.2<br>G.3                             | Diagram of high speed package for use with MIT-OEIC-8 and MIT-OEIC-9.       457         Layout plot of MIT-OEIC-8       459         Unit cell of the MIT-OEIC-8 receiver array       460                                                                                                                                   |

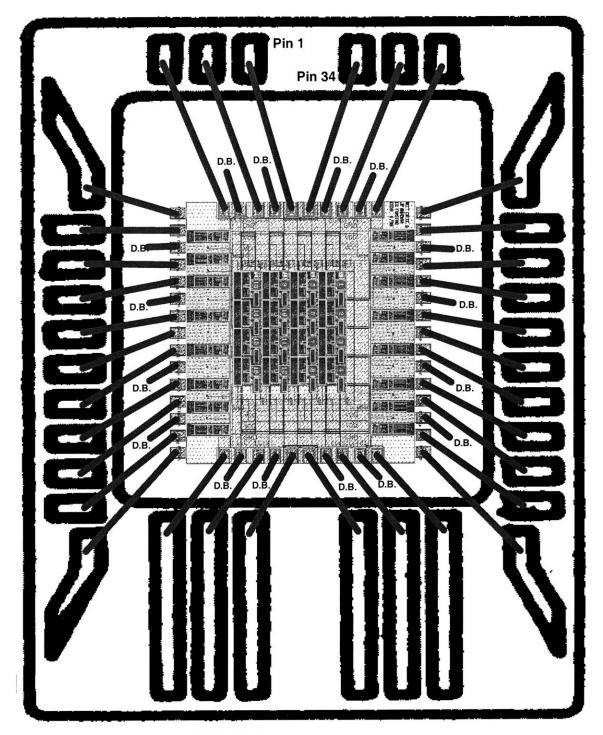

| G.4                                           | Bonding diagram for MIT-OEIC-8                                                                                                                                                                                                                                                                                             |

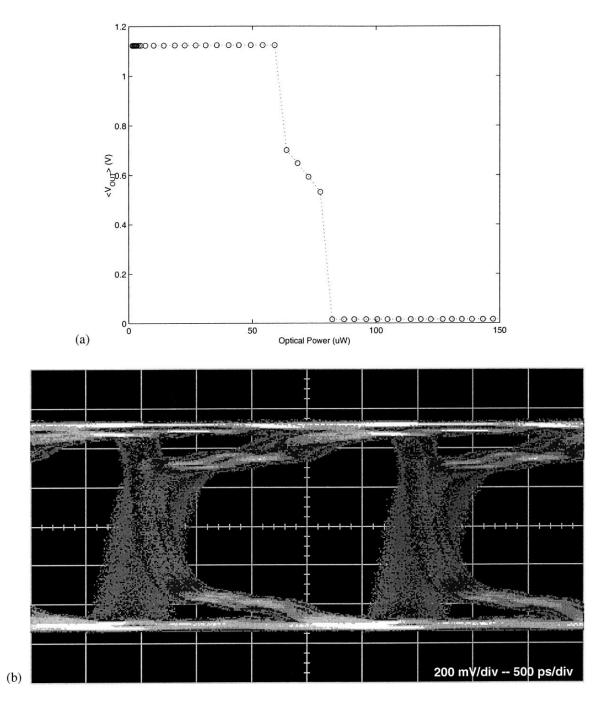

| G.5                                           | Typical characteristics from MIT-OEIC-8                                                                                                                                                                                                                                                                                    |

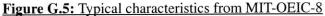

| G.6                                           | Layout plot of MIT-OEIC-9                                                                                                                                                                                                                                                                                                  |

| G.7                                           | Unit cell of MIT-OEIC-9 receiver array                                                                                                                                                                                                                                                                                     |

| G.8                                           | Bonding diagram for MIT-OEIC-9                                                                                                                                                                                                                                                                                             |

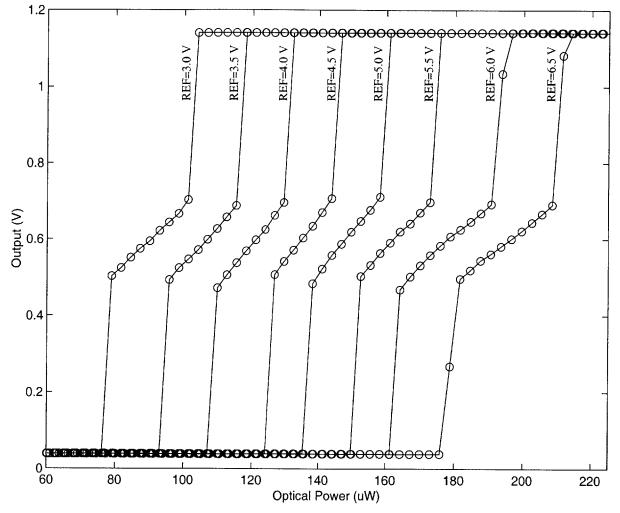

| G.9                                           | Static characteristics from MIT-OEIC-9                                                                                                                                                                                                                                                                                     |

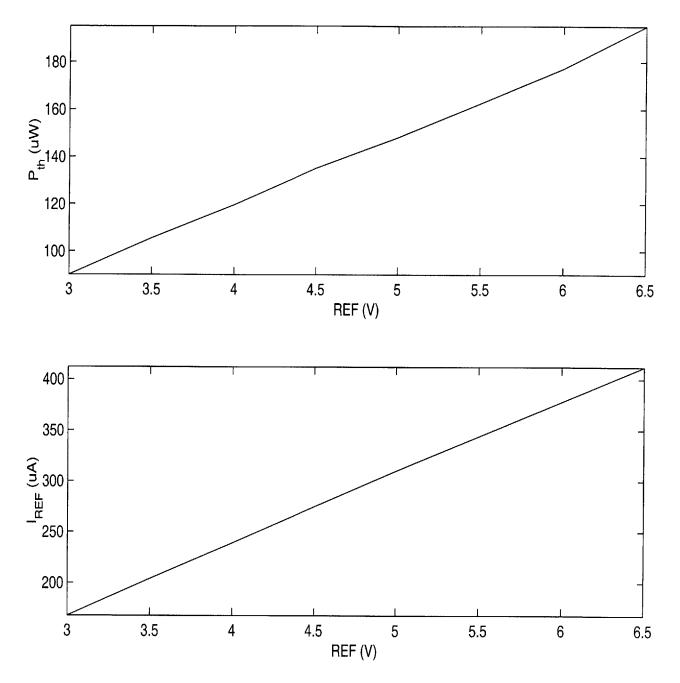

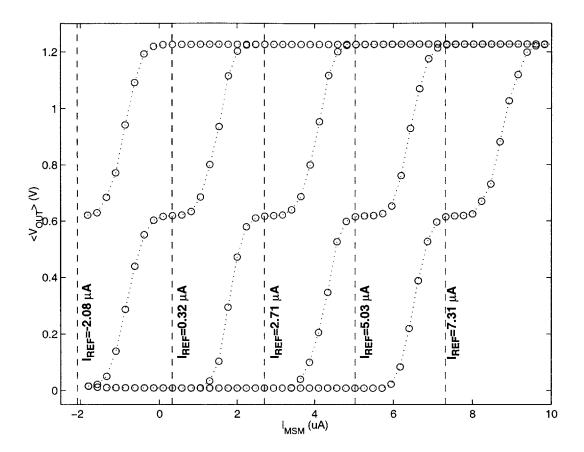

| G.10                                          | Plots of Pth and IREF vs. the REF voltage                                                                                                                                                                                                                                                                                  |

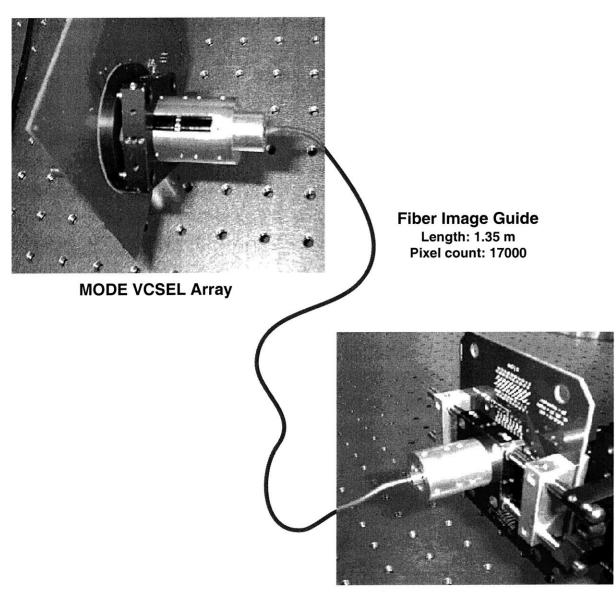

| G.11                                          | Optical link demonstration using MIT-OEIC-9                                                                                                                                                                                                                                                                                |

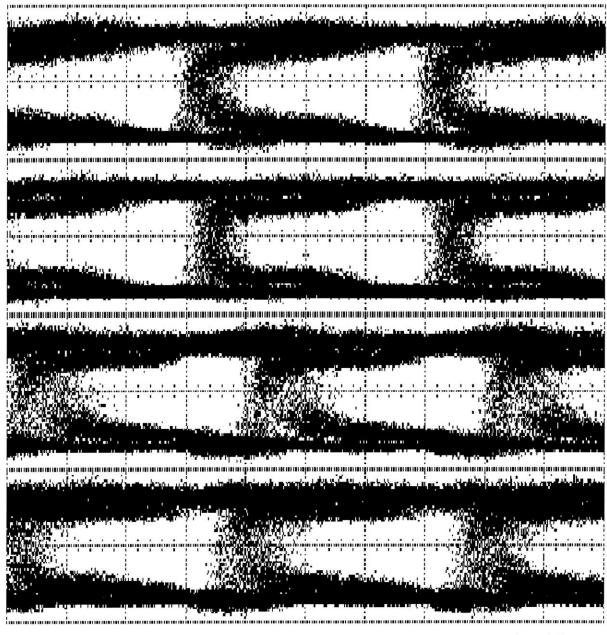

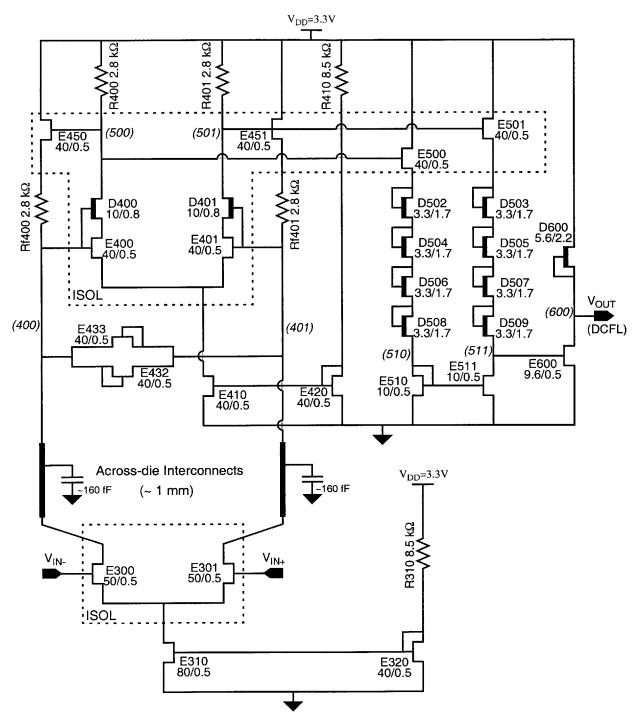

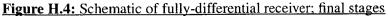

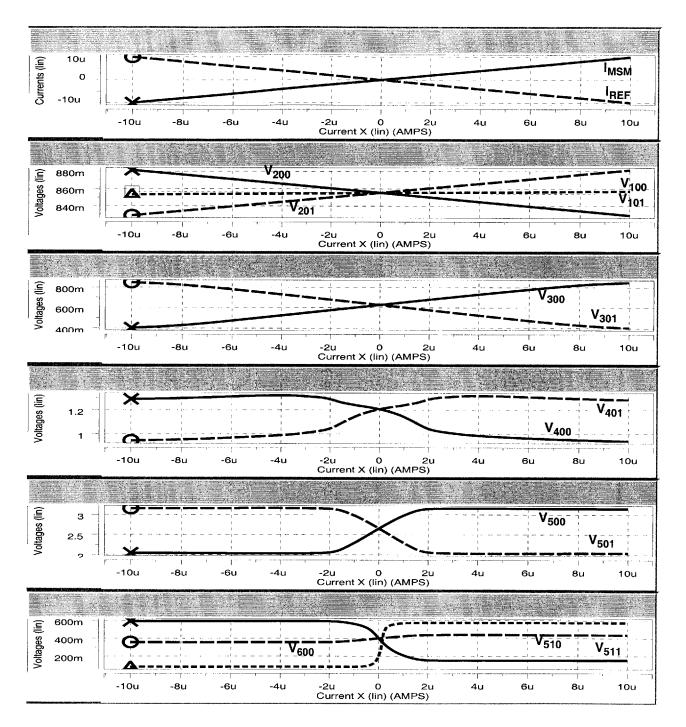

| G.12                                          | Parallel data transmission using MIT-OEIC-9                                                                                                                                                                                                                                                                                |